Slik bruker du Efinix FPGA-er for AI/ML-avbildning – Del 1: Komme i gang

Bidrag fra DigiKey's European Editors

2023-04-20

Redaktørens merknad: Nye tilnærminger til FPGA-arkitekturer gir mer detaljert styring og økt fleksibilitet for å møte behovene til maskinlæring (ML) og kunstig intelligens (AI). Del 1 av denne todelte serien introduserer en slik arkitektur fra Efinix og viser hvordan man kommer i gang med denne ved å bruke et utviklingskort. Del 2 omhandler forbindelsen mellom utviklingskortet og eksterne enheter og periferiutstyr, for eksempel et kamera.

FPGA-er spiller en avgjørende rolle i mange konstruksjoner, fra industriell styring og sikkerhet til robotikk, romfart og bilindustrien. Takket være den fleksible naturen til den programmerbare logikkjernen og de brede tilkoblingsegenskapene, ligger ett voksende brukstilfelle for FPGA-er i bildebehandling når ML-inferens skal distribueres. FPGA-er er ideelle for å implementere løsninger som har flere høyhastighets kameragrensesnitt. I tillegg muliggjør FPGA-er også implementering av dedikerte prosesserings-pipeliner i logikken, og fjerner derved flaskehalser som ville være forbundet med CPU- eller GPU-baserte løsninger.

Konstruksjonene til mange utviklere krever imidlertid mer ML/AI-funksjonalitet og mer finkornet styring eller ruting og logikk, utover hva klassiske FPGA-arkitekturer med kombinatoriske logikkblokker (CLB – combinatorial logic block) kan gi. Nyere tilnærminger til FPGA-arkitekturer adresserer disse problemene. For eksempel bruker Efinix sin Quantum-arkitektur en eXchangeable Logic and Routing (XLR – eXchangeable Logic and Routing)-blokk.

Denne artikkelen tar for seg viktige funksjoner og egenskaper i Efinix FPGA-arkitekturen, og legger vekt på egne AI/ML-muligheter og presenterer implementeringer gjort i den virkelige verden. Den tar deretter for seg et utviklingskort og tilknyttede verktøy som utviklere kan bruke til å raskt komme i gang med sin neste AI/ML-avbildningskonstruksjon.

Efinix FPGA-enheter

Efinix tilbyr for tiden to sortimenter av enheter. Den introduserte opprinnelig Trion-familien, som tilbyr logiske tettheter fra 4000 (4K) til 120K logiske elementer (LE-er), og er produsert ved hjelp av en SMIC 40LL-prosess. Den nyeste enhetslinjen, Titan-familien, tilbyr logiske tettheter fra 35K til 1 million (1M) logiske elementer, og er produsert på den svært populære TSMC-noden på 16 nanometer (nm).

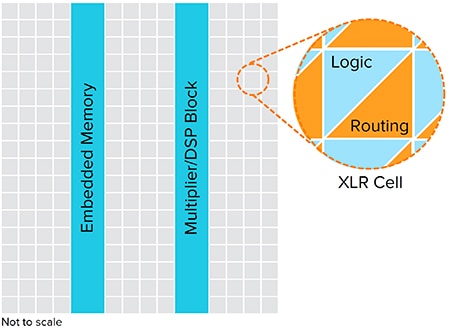

Begge tilbudene er basert på Quantum-arkitekturen, som er unik i FPGA-verdenen. Den standard FPGA-arkitekturen er basert på CLB-er, som på det enkleste nivået inneholder en oppslagstabell (LUT – look-up table) og flipflop-er. CLB-ene implementerer logiske ligninger som deretter sammenkobles via ruting. Efinix sin Quantum-arkitektur beveger seg bort fra distinkte logikk- og rutingsblokker med XLR-blokken.

Det som gjør en XLR-blokk unik, er at den kan konfigureres til å fungere som en logisk celle med en LUT, et register og en adderer eller en rutingsmatrise. Denne tilnærmingen tilbyr en finkornet arkitektur som gir rutingsfleksibilitet, noe som gjør det mulig for implementeringer som er logisk tunge eller rutingstunge å oppnå ønsket ytelse.

Figur 1: Det som gjør en XLR-blokk unik, er at den kan konfigureres til å fungere som enten en logisk celle med en LUT, et register og en adderer eller en rutingsmatrise. (Bildekilde: Efinix)

Figur 1: Det som gjør en XLR-blokk unik, er at den kan konfigureres til å fungere som enten en logisk celle med en LUT, et register og en adderer eller en rutingsmatrise. (Bildekilde: Efinix)

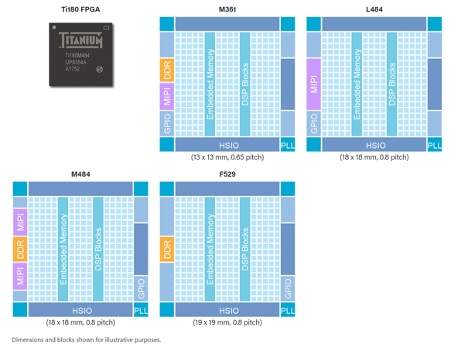

Som den nyeste familien, tilbyr Titanium-enhetene de mest avanserte funksjonene for utvikleren (figur 2). Sammen med XLR-kjernen, gir de serielle koblinger på flere gigabit som fungerer ved enten 16 gigabit per sekund (Gb/s) eller 25,8 Gb/s, avhengig av hvilken enhet som er valgt. Disse koblingene på flere gigabit er avgjørende for å muliggjøre høyhastighets dataoverføring på og utenfor brikken.

Figur 2: Titanium FPGA Ti180 kommer i en rekke alternativer, avhengig av bussens bredde, I/O og minnekrav. (Bildekilde: Efinix)

Figur 2: Titanium FPGA Ti180 kommer i en rekke alternativer, avhengig av bussens bredde, I/O og minnekrav. (Bildekilde: Efinix)

Titanium-enheter gir også et bredt spekter av grensesnittfunksjoner for inngang/utgang (I/O) som kan grupperes som generell I/O (GPIO), og som kan støtte enkeltsidige I/O-standarder som lavspent CMOS (LVCMOS) ved 3,3 volt, 2,5 volt og 1,8 volt.

For grensesnitt med høy hastighet og differensialgrensesnitt, gir Titanium-enhetene høyhastighets I/O (HSIO) som støtter ensidige (single-ended) I/O-standarder som LVCMOS på 1,2 volt, 1,5 volt og SSTL og HSTL. Differensielle I/O-standarder som støttes av HSIO inkluderer differensiell signalering med lav spenning (LVDS – low-voltage differential signaling), differensiell SSTL og HSTL.

Moderne FPGA-er krever også et nært koblet minne med høy båndbredde, som brukes til å lagre bilderammer for bildebehandlingskonstruksjoner, samplingsdata for signalbehandling og selvfølgelig til å kjøre operativsystemer og programvare for prosessorer implementert i FPGA-en. Titanium-utvalget av enheter gir muligheten til å koble sammen med DDR4 (dynamic data rate 4) og laveffekts DDR4(x) (LPDDR4(x)). Avhengig av den nøyaktige Titanium-enheten som er valgt, er bussbreddestøtten x32 (J) eller x16 (M), og noen enheter har ikke LPDDR4-støtte (L).

Titanium FPGA-er er SRAM-baserte og krever et konfigurasjonsminne, der enhetskonfigurasjonen utføres av enten master/slave-SPI (Serial Peripheral Interconnect) eller JTAG. For å sikre at denne konfigurasjonsmetoden er sikker, bruker Titanium FPGA-en AES GCM-kryptering av bitstrømmen, i tillegg til AES GCM og RSA-4096 for å gi bitstrømautentisering. Høy sikkerhet som dette er nødvendig siden FPGA-er er distribuert på kanten der ondsinnede aktører kan få tilgang til og manipulere oppførselen.

Introduksjon til utviklingskort

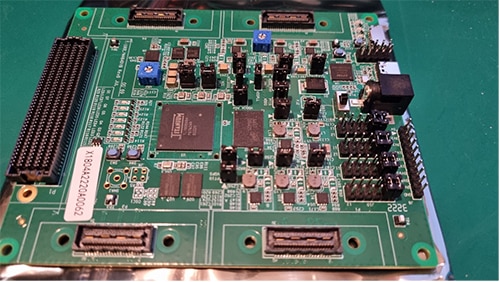

Utviklingskort utgjør et kritisk element i FPGA-evalueringsprosessen, siden de kan brukes til å utforske egenskapene til en enhet og prototypekonstruksjoner, og dermed bidra til å redusere den generelle risikoen. Det første utviklingskortet som er tilgjengelig for å evaluere Titanium FPGA-er og begynne prototyping av konstruksjoner, er Ti180 M484 (figur 3). Kortet har en FMC-kontakt (FMC – FPGA Mezzanine Card) og fire Samtec QSE-kontakter.

Figur 3: Sammen med en Titanium FPGA, har Ti180 M484-utviklingssettet en FMC-kontakt og fire Samtec QSE-kontakter. (Bildekilde: Adam Taylor)

Figur 3: Sammen med en Titanium FPGA, har Ti180 M484-utviklingssettet en FMC-kontakt og fire Samtec QSE-kontakter. (Bildekilde: Adam Taylor)

Ti180 FPGA-en som er montert på dette utviklingskortet gir 172K XLR-celler, 32 globale klokker, 640 digitale signalbehandlingselementer (DSP-elementer) og 13 megabit (Mb) innebygd RAM. DSP-elementene gir muligheten til å implementere 18 x 19 multiplikasjoner med faste punkt og 48-bits multiplikasjoner. Denne DSP-en kan også optimaliseres for SIMD-operasjoner (SIMD – single instruction, multiple data) som kjører i enten dobbel eller firedobbel konfigurasjon. DSP-elementer kan også konfigureres til å utføre flytetallshandlinger.

I likhet med de fleste andre utviklingskortene, kommer Ti180-utviklingskortet med enkle lysdioder og knapper. Den virkelige kraften til dette utviklingskortet ligger imidlertid i grensesnittfunksjonene. Ti180-utviklingskortet har en FMC-kontakt med lavt pinneantall som gjør det mulig å koble til et bredt spekter av eksterne enheter. Siden det er en mye brukt standard, er det mange FMC-kort som muliggjør sammenkobling av høyhastighets analog-til-digital-omformer (ADC), digital-til-analog-omformer (DAC), nettverk og minne/lagringsløsninger.

I tillegg til FMC-tilkoblingen, har kortet fire Samtec QSE-kontakter som gjør det mulig for utviklere å legge til utvidelseskort. Disse QSE-kontaktene brukes til å gi MIPI-innganger og -utganger, der hver QSE-kontakt gir enten en MIPI-inngang eller MIPI-utgang.

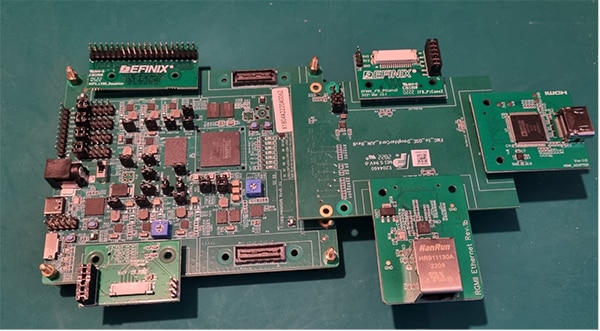

Figur 4: Ti180 M484-utviklingssettet vises med sitt allsidige utvalg av utvidelsesalternativer basert på QSE- og FMC-kontakter. (Bildekilde: Adam Taylor)

Figur 4: Ti180 M484-utviklingssettet vises med sitt allsidige utvalg av utvidelsesalternativer basert på QSE- og FMC-kontakter. (Bildekilde: Adam Taylor)

Ti180-kortet gir også 256 Mb LPDDR4 for å støtte minnet med høy ytelse som kreves i bilde- eller signalbehandlingskonstruksjoner. I tillegg gir utviklingskortet en rekke klokkealternativer ved 25; 33,33; 50 og 74,25 megahertz (MHz), som kan brukes med enhetens faselåsesløyfe (PLL – phase lock loop) for å generere forskjellige interne frekvenser.

Muligheten til å omprogrammere og feilsøke kortet i sanntid under utvikling er kritisk og krever en JTAG-tilkobling, som gis på kortet via et USB-C-grensesnitt. Det er også tilveiebrakt ikke-flyktig minne i form av to 256 Mb NOR-flash-enheter som kan brukes til å demonstrere konfigurasjonsløsningen.

Kortet er drevet fra en 12-volts universell strømadapter som er inkludert i boksen. Et FMC-til-QSE-utbrytningskort er også inkludert, i tillegg til QSE-baserte utvidelseskort for HDMI, Ethernet, MIPI og LVDS. For å demonstrere bildebehandlingsegenskapene til Ti180, tilbys også et dobbelt RPI-datterkort og to IMX477-kamerakort.

Programvaremiljøet

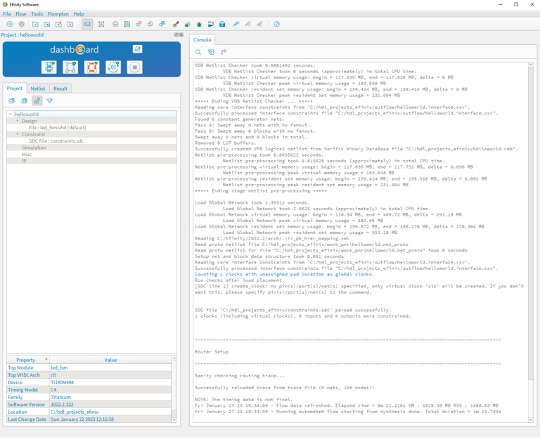

Implementering av konstruksjoner rettet mot Ti180-utviklingskortet, bruker Efinix-programvaren Efinity. Programvaren gjør det mulig å generere en bitstrøm via syntese, sted og rute. Det gir også utviklere blokkeringer for immaterielle rettigheter (IP), timinganalyse og feilsøking på brikke.

Vær oppmerksom på at et utviklingskort er nødvendig for å få tilgang til Efinity-programvaren. I motsetning til andre leverandører, har ikke verktøyet forskjellige versjoner som krever ekstra lisensiering.

Innenfor Efinity opprettes nye prosjekter rettet mot den valgte enheten. RTL-filer kan deretter legges til i prosjektet, i tillegg til begrensninger opprettet for timing og I/O-konstruksjon. Det er innenfor Efinity at utviklere også er i stand til å implementere I/O-konstruksjon ved å bruke HSIO, GPIO og spesialisert I/O.

Figur 5: Innenfor Efinity opprettes nye prosjekter rettet mot den valgte enheten. (Bildekilde: Adam Taylor)

Figur 5: Innenfor Efinity opprettes nye prosjekter rettet mot den valgte enheten. (Bildekilde: Adam Taylor)

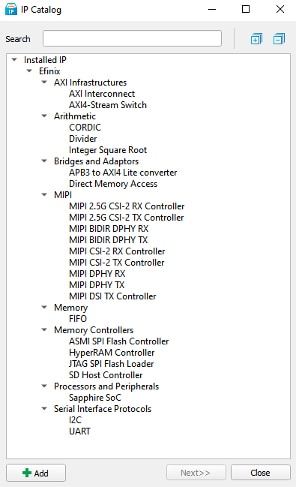

Et kritisk element i FPGA-konstruksjon er å utnytte IP, spesielt for komplekse IP-er som AXI-sammenkoblinger, minnekontrollere og softcore-prosessorer. Efinity gir utviklere en rekke IP-blokker som kan brukes til å akselerere konstruksjonsprosessen.

Figur 6: Efinity gir utviklere en IP-katalog som de kan bruke til å akselerere konstruksjonsprosessen. (Bildekilde: Adam Taylor)

Figur 6: Efinity gir utviklere en IP-katalog som de kan bruke til å akselerere konstruksjonsprosessen. (Bildekilde: Adam Taylor)

Mens FPGA-er er gunstige for å implementere parallelle prosesseringsstrukturer, inkluderer mange FPGA-konstruksjoner softcore-prosessorer. Disse gir muligheten til å implementere sekvensiell prosessering, slik som nettverkskommunikasjon. For å muliggjøre distribusjon av softcore-prosessorene i Efinix-enhetene, tilbyr Efinity system på brikke (SoC – system-on-chip)-konfigurasjonsverktøyet Sapphire. Sapphire gjør det mulig for utviklere å definere et flerprosessorsystem som har både hurtigbuffere og hurtigbufferkoherens på tvers av flere prosessorer, samt muligheten til å kjøre et integrert Linux-operativsystem. I Sapphire kan utviklere velge mellom én og fire softcore-prosessorer.

Softcore-prosessoren som implementeres er den myke VexRiscV-prosessoren, som er basert på arkitekturen for RISC-V-instruksjonssett. VexRiscV-prosessoren er en 32-bits implementering som har utvidelser for «pipelining» og tilbyr et konfigurerbart funksjonssett, noe som gjør den ideell for implementering i Efinix-enheter. Valgfrie konfigurasjoner inkluderer en multiplikator, atominstruksjoner, flytepunktutvidelser og komprimerte instruksjoner. Avhengig av konfigurasjonen av SoC-systemet, vil ytelsen variere mellom 0,86 og 1,05 DMIPS/MHz.

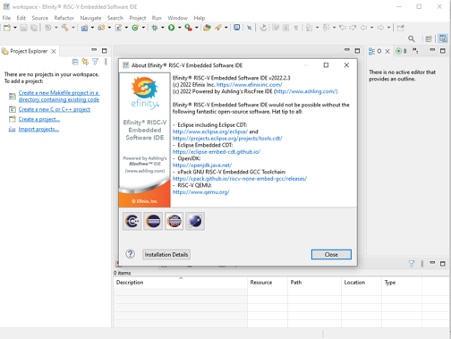

Når maskinvaremiljøet er konstruert og implementert i Efinix-enheten, kan konstruksjonens programvare utvikles ved å bruke Ashling RiscFree IDE-en. Ashling RiscFree er en Eclipse-basert IDE som gjør det mulig å lage og kompilere applikasjonsprogramvare, sammen med feilsøking på målet for å finjustere applikasjonen før distribusjon.

Figur 7: Ashling RiscFree er en Eclipse-basert IDE som gjør det mulig å lage og kompilere applikasjonsprogramvare, sammen med feilsøking på målet. (Bildekilde: Adam Taylor)

Figur 7: Ashling RiscFree er en Eclipse-basert IDE som gjør det mulig å lage og kompilere applikasjonsprogramvare, sammen med feilsøking på målet. (Bildekilde: Adam Taylor)

Hvis en innebygd Linux-løsning utvikles, leveres alle nødvendige oppstartsgjenstander (boot artifacts), for eksempel First Stage Boot Loader, OpenSBI, U-Boot og Linux ved hjelp av Buildroot. Alternativt kan utvikleren bruke FreeRTOS hvis en sanntidsløsning er nødvendig.

AI-implementering

Efinix sin AI-implementering bygger på RISC-V-softcore-operasjonen. Den tilpassede instruksjonskapasiteten til RISC-V-prosessoren dras nytte av for å muliggjøre akselerasjon av TensorFlow Lite-løsninger. Bruken av RISC-V-prosessoren gjør det også mulig for brukere å lage egendefinerte instruksjoner som kan brukes som en del av forhåndsprosessering eller etterprosessering etter AI-inferensen, noe som skaper en mer responsiv og deterministisk løsning.

For å komme i gang med en AI-implementering, er det første trinnet å utforske Efinix Model Zoo, som er et bibliotek med AI/ML-modeller optimalisert for slutteknologien. Utviklere som arbeider med Efinix-enhetene kan få tilgang til Model Zoo, og nettverket kan opplæres ved hjelp av Jupyter Notebooks eller Google Colab. Når nettverket har blitt trent, kan det konverteres fra en flytepunktsmodell til en kvantisert modell ved å bruke TensorFlow Lite-omformeren.

I TensorFlow Lite-formatet, kan Efinix sin tinyML-akselerator brukes til å lage en distribuerbar løsning på RISC-V-løsningen. tinyML-generatoren gjør det mulig for utviklere å tilpasse akseleratorimplementeringen og generere prosjektfilene. Når den distribueres på denne måten, kan akselerasjonen variere mellom 4 og 200 ganger, avhengig av den valgte arkitekturen og tilpassingen.

Konklusjon

Efinix-enheter gir utviklere fleksibilitet, takket være deres unike XLR-arkitektur. Verktøykjeden muliggjør implementering av RTL-konstruksjon, i tillegg til implementering av komplekse SoC-løsninger som distribuerer RISC-V-prosessorer med programvare. En AI/ML-løsning som muliggjør distribusjon av ML-inferens, bygges på softcore SoC-en.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.