Implementer lavstrøms, høyytelses Edge-databehandling med Efinx' Quantum-aktiverte FPGA-er

Bidrag fra DigiKeys nordamerikanske redaktører

2020-03-17

Klassisk skydatabehandling har problemer med ventetid, datasikkerhet, sluttbrukerens personvern, tilgjengelig båndbredde og pålitelig tilkobling. Utviklere og systemarkitekter ser mot Edge-databehandling for å håndtere disse problemene. Men Edge-databehandling har også enkelte utfordringer, alt fra kostnader, størrelse, ytelse og strømforbruk til problemer med skalerbarhet, fleksibilitet og oppgradering. Dette gjelder spesielt når utviklere vil utføre mer bildebehandling og implementere flere algoritmer for kunstig intelligens (AI) og maskinlæring (ML) nærmere datakilden.

Som et resultat ser utviklere etter noe annet enn tradisjonelle mikrostyringer (MCU-er) eller programbehandlere (AP-er) og vurderer feltprogrammerbare portmatriser (FPGA-er) med tilhørende parallelle behandlingsmulighetene. Regelmessige forbedringer i designet og implementeringen av FPGA-er betyr at de nå kan oppfylle mange av eller alle disse kravene – enten som frittstående enheter, eller i sammen med MCU-er og AP-er. Når det er sagt, er det mange utviklere som ikke er kjent med FPGA-er, og som er bekymret for læringskurven.

Denne artikkelen gir en kort innføring i migreringen fra sky- til Edge-databehandling og hvorfor tradisjonelle behandlingsarkitekturer ikke strekker til når det gjelder bildebehandling, AI og ML. Den tar deretter en rask titt på FPGA-er og hvorfor de har en arkitektonisk fordel over disse dataintensive Edge-programmene. Til slutt introduserer den en ny tilnærming til FPGA-er – Quantum-teknologi fra Efinix – og hvordan du bruker den.

Hvorfor Edge-databehandling?

I tradisjonell skydatabehandling hentes data fra utallige eksterne plasseringer og mates inn i et skybasert system for lagring og analyse. Det er imidlertid mange ulemper med denne tilnærmingen. Disse inkluderer kostnadene ved å overføre store mengder rådata, opprettholde integriteten og sikkerheten til disse dataene når de overføres, ventetid ved svar, bekymringer for sluttbrukerens personvern, ofte upålitelige Internett-tilkoblinger samt bruk av tilgjengelig båndbredde som ikke er helt optimal.

Edge-databehandling betyr at vi kan flytte behandlingen – beregning og analyse – nærmere kanten av Internett hvor dataene genereres, analyseres, samles inn og brukes. Begrepet Edge-databehandling er ikke spesifikt for et bruksområde eller en enhet, og utviklere kan velge kun Edge-behandling eller en kombinasjon av skyen og Edge, etter behov.

Edge-bruksområder inkluderer blant annet smarte fabrikker, smarte byer, smarte hjem og smart transport. Edge-enheter kan variere fra store, avanserte Edge-servere til relativt små sensor- og aktuatorsystemer som er plassert på ytterste Edge av Internett – på datagenereringspunktet.

Fordelen med FPGA-er

Når det gjelder beregningen, er tradisjonelle prosessorer svært effektive når det kommer til beslutningstaking og sekvensielle oppgaver, men er veldig ineffektivt når det gjelder mange databehandlingsalgoritmer, slik som de som brukes til bildebehandling, AI og ML. Disse oppgavene kan ofte deles opp i svært parallelle (versus sekvensielle) behandlingstrinn. Når dette skjer, er det nettopp disse programmene som migrerer til Edge og ytterste Edge.

Det faktum at FPGA-er kan programmeres (konfigureres) for å implementere en kombinasjon av funksjoner, gjør at de kan utføre bildebehandlings-, AI- og ML-algoritmer på en svært parallell måte, og dermed minimere ventetiden og samtidig redusere strømforbruket. I tillegg til de viktigste programmerbare materialene, er FPGA-er utstyrt med digitale signalbehandlingsblokker (DSP) på brikken (chip-en) som inneholder spesielle multiplikatorer som øker hastigheten på DSP-intensive programmer. FPGA-er har også minneblokker på brikken som forenkler prosessorbehandlingen på brikken, noe som er mye raskere enn å ikke bruke brikken.

Det finnes flere FPGA-leverandører, hver med sine egne unike tilbud. Én av disse leverandørene, Efinix, har utviklet en spesiell FPGA-arkitektur kalt Quantum, og som er unikt egnet for Edge-databehandling generelt, og særlig bildebehandling. Trion-serien med FPGA-er (og Quantum ASICs) er basert på denne teknologien og leverer et fire ganger forbedret strømytelsesområde sammenlignet med tradisjonelle FPGA-teknologier (figur 1). Efinitys integrerte utviklingsmiljø (IDE) sammenkobler FPGA- og ASIC-domener.

Figur 1: Med et fordelsmessig strømytelsesområde kan Trion FPGA-er håndtere programmer så som tilpasset logikk, beregningsakselerasjon, ML, dyp læring og bildebehandling. Med Efinity IDE kan brukere migrere sømløst fra en Trion FPGA til en Quantum ASIC for svært høy volumproduksjon. (Bildekilde: Efinix)

Figur 1: Med et fordelsmessig strømytelsesområde kan Trion FPGA-er håndtere programmer så som tilpasset logikk, beregningsakselerasjon, ML, dyp læring og bildebehandling. Med Efinity IDE kan brukere migrere sømløst fra en Trion FPGA til en Quantum ASIC for svært høy volumproduksjon. (Bildekilde: Efinix)

Hva er Quantum-teknologi?

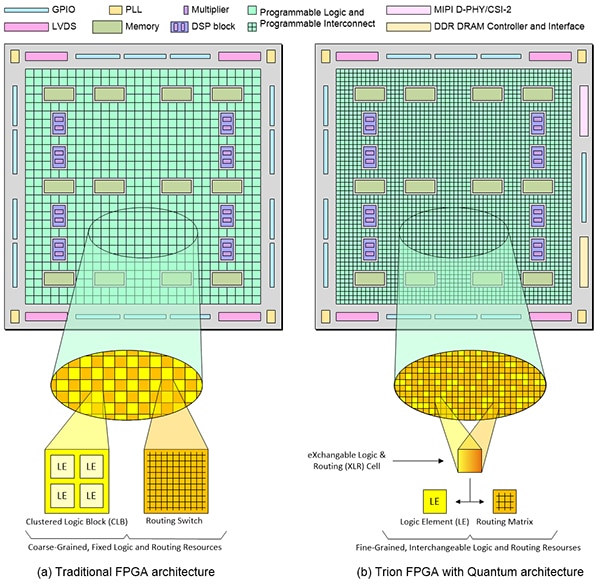

I likhet med tradisjonelle FPGA-er, inkluderer Trion FPGA-er minne- og DSP-blokker. Forskjellen ligger i det programmerbare materialet (figur 2). Logikkelementet (LE) er kjernen til programmerbar logikk. Hvert logikkelement (LE) inkluderer en oppslagstabell (LUT), en multiplekser og et register, som alle kan konfigureres etter behov. Når det gjelder tradisjonelle FPGA-er, kan det programmerbare materialet beskrives som «grovkornet».

Figur 2: En tradisjonell FPGA-arkitektur (A) er grovkornet, og selv om logikken og sammenkoblingen er programmerbare, er de fremdeles faste ressurser. Trion FPGA-er (b) som er basert på Quantum-arkitekturen, er finkornet i forhold, og logikk- og føringsressursene er utskiftbare (Bildekilde: Max Maxfield)

Figur 2: En tradisjonell FPGA-arkitektur (A) er grovkornet, og selv om logikken og sammenkoblingen er programmerbare, er de fremdeles faste ressurser. Trion FPGA-er (b) som er basert på Quantum-arkitekturen, er finkornet i forhold, og logikk- og føringsressursene er utskiftbare (Bildekilde: Max Maxfield)

I grovkornede materialer samles flere logikkelementer sammen til en større klynget logikkblokk (CLB). Vær oppmerksom på at noen leverandører bruker begrepet konfigurerbar logikkblokk (CLB), og andre bruker logisk matriseblokk (LAB), men det betyr det samme.

Det er viktig å merke seg at denne illustrasjonen er en abstraksjon. CLB-er og føringsbrytere (programmerbar sammenkobling) i tradisjonelle FPGA-er presenteres egentlig ikke i et sjakkbrettmønster som vist her. De er imidlertid faste og uforanderlige, da den programmerbare logikken alltid kommer til å være programmerbar logikk, og den programmerbare sammenkoblingen alltid kommer til å være programmerbar sammenkobling.

Sammenlignet med tradisjonelle arkitekturer, er Trion FPGA-er mer finkornet, helt ned til oppløsningen av et enkelt logikkelement. I tillegg kan alle utskiftbare logikk- og føringsceller (XLR) konfigureres til å fungere som et logikkelement eller som en del av føringsmatrisen.

Konfigurasjonscellene som brukes i Quantum-arkitektur, er SRAM-basert, som betyr at denne teknologien er «silisiumagnostisk». De kan produseres ved hjelp av en standard CMOS-prosess uten behov for spesielle behandlingstiltak som er nødvendige for alternative konfigurasjonsteknologier, som blits og antisikring, som brukes i noen mellom-FPGA-er.

Denne programvarekonfigurerbare logikken og føringen samt tilpassbare sammenkoblingen med høy ytelse gir den Quantum-baserte tilnærmingen et fire ganger forbedret strømytelsesområde (PPA) sammenlignet med tradisjonelle SRAM-baserte FPGA-er som er opprettet i samme prosessteknologinode.

FPGA-er som er opprettet med Quantum-arkitekturen, krever også bare sju metalliseringslag, i motsetning til de over tolv lagene som er nødvendige i tradisjonelle FPGA-er. Siden hvert ekstra lag med metall krever flere maske- og prosesstrinn, reduseres design- og produksjonskostnader samt at avkastningen økes hvis du kun bruker syv lag.

Alle disse egenskapene og funksjonene er svært nyttige for utviklere som ser etter kostnads-, størrelses-, ytelses- og fleksibilitetsfordeler for Edge-databehandling og bildebehandling. Trion FPGA-er er derfor ideelle for både tradisjonelle FPGA-programmer og til fremvoksende Edgedatabehandlings- og bildebehandlingsprogrammer. Sistnevnte inkluderer mobil, IoT (Internet of Things), automasjon, robotikk, sensorfusjon, datamaskinvisjon, AI og ML.

Strukturen til Trion FPGA-er

Trion FPGA-er produseres med en lavstrøms silisiumprosess på 40 nanometer (nm), med mellom 4000 (K) og 200 000 (K) logikkelementer, selv om prosessen er skalerbar for mye større enheter. Alle Trion FPGA-er inkluderer minne- og DSP-blokker, men kapasiteten og antallet varierer etter størrelsen på enheten. Mindre enheter som T4F81C2 har mer minimalistiske funksjoner (dvs. 3888 LE-er, 78 848 minnebiter, 59 GPIO-er) og er rettet mot håndholdte kontrollplanfunksjoner.

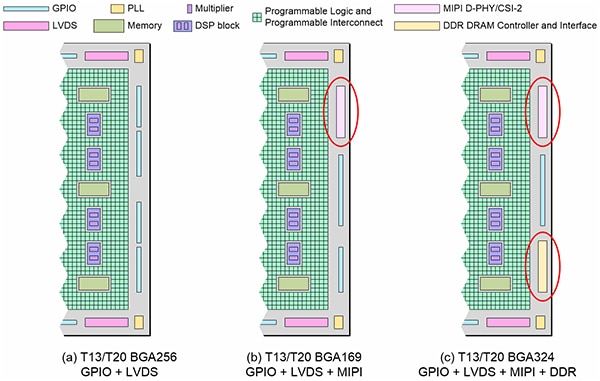

Avanserte enheter som T20F256C3 inneholder også flere ressurser (dvs. 19 728 logikkelementer, 1 069 548 minnebiter, 195 GPIO-er). T13F256C3 ligner på T20F256C3, men har 12 828 logikkelementer. Enheter som T13/T20 kommer i ulike versjoner (figur 3).

Figur 3: Efinix T13/T20 BGA256s (a) er en generisk FPGA som er et godt valg for design med I/O-intensive behov. T13/T20 BGA169s (b) inkluderer to MIPI D-PHY/CSI-2 hardkjerneblokker for design som støtter MIPI-kameragrensesnittet, og T13/T20 BGA324s (c) utvider MIPI-grensesnittene med et hardkjernet x16-bit DRAM-grensesnitt med dobbel datahastighet (DDR), og styring for design med intensive behov for minnebåndbredde. (Bildekilde: Max Maxfield)

Figur 3: Efinix T13/T20 BGA256s (a) er en generisk FPGA som er et godt valg for design med I/O-intensive behov. T13/T20 BGA169s (b) inkluderer to MIPI D-PHY/CSI-2 hardkjerneblokker for design som støtter MIPI-kameragrensesnittet, og T13/T20 BGA324s (c) utvider MIPI-grensesnittene med et hardkjernet x16-bit DRAM-grensesnitt med dobbel datahastighet (DDR), og styring for design med intensive behov for minnebåndbredde. (Bildekilde: Max Maxfield)

MIPI CSI-2 er det mest brukte kameragrensesnittet i mobilmarkedet og i andre markeder på grunn av den lave strømforsyningen, korte ventetiden og lavkostnads brikke-til-brikke-tilkobling. Den støtter også et stort utvalg høyytelsesformater, inkludert 1080p, 4K, 8K (og høyere) video, i tillegg til bildebehandling med høy oppløsning. Det du kan legge merke til her er det faktum at MIPI CSI-2 er det dominerende grensesnittet som brukes for visjonssensorer i Edge-programmer. T13/T20 BGA169s FPGA-er inkluderer to MIPI D-PHY/CSI-2-hardkjerneblokker for å støtte designene i disse programmene (figur 3, igjen).

DDR-minne støtter dataoverføringer med høy båndbredde, men det krever også tilslutning til en streng timing-protokoll. I tillegg til et herdet MIPI D-PHY/CSI-2-grensesnitt, har Trion-T13/T20 BGA324s (figur 3, igjen) også et herdet x16-bit DDR DRAM-grensesnitt, og styring for design med intensive behov for minnebåndbredde.

Quantum ASICs

Som tidligere nevnt, er konfigurasjonscellene som brukes i Trion FPGA-er, SRAM-baserte. Trion FPGA-er må, som et resultat av dette, ha konfigurasjonsdataene lastet inn, enten fra en ekstern minneenhet eller via «bit-banging» på vertsbehandleren, når enheten starter. Efinix tilbyr også løsninger for Quantum-akselerert innebygd FPGA (eFPGA) i form av Quantum ASICs, for å utføre dette med svært høy volumproduksjon. I dette tilfellet kan Efinix ta T4-, T8-, T13- eller T20-design og opprette maskeprogrammerte Quantum ASIC-versjoner som starter internt, uten at du trenger en ekstern konfigurasjonsenhet.

Design og utvikling med Trion FPGA-er

Med Efinix får du en rekke evalueringskort og utviklingssett, slik at du kan bli kjent med Trion FPGA-er. Disse inkluderer Trion T8F81C-DK T8 Trion FPGA-utviklingssett, Trion T20F256C-DK T20 Trion FPGA-evalueringskort og Trion T20 MIPI-DK T20 MIPI D-PHY/CSI-2-utviklingssett.

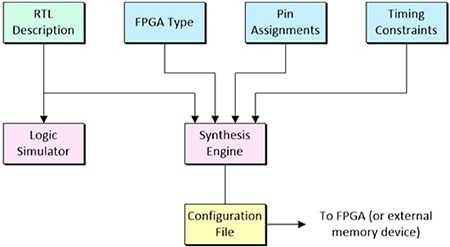

En av de vanligste teknikkene som brukes til å utvikle med FPGA-er, kalles språkdrevet design (LDD). Dette inkluderer å registrere designintensjonen på et abstraksjonsnivå som kalles registrert overføringsnivå (RTL) ved å bruke et språk for maskinvarebeskrivelse (HDL), for eksempel Verilog eller VHDL. Etter bekreftelse via logikksimulering, mates denne representasjonen inn i en syntesemotor, sammen med ytterligere informasjon som FPGA-måltype, pinneoppgaver og tidsbegrensninger, for eksempel maksimale inngang-til-utgang-forsinkelser. Resultatet fra syntesemotoren er en konfigurasjonsfil som lastes direkte inn i FPGA eller inn i en ekstern minneenhet (figur 4).

Figur 4: etter verifisering via logikksimulering, mates RTL-designbeskrivelsen inn i en syntesemotor, sammen med ytterligere designdetaljer, som FPGA-type, pinneoppgaver og tidsbegrensninger. Resultatet fra syntesemotoren er en konfigurasjonsfil som lastes inn i FPGA-en. (Bildekilde: Max Maxfield)

Figur 4: etter verifisering via logikksimulering, mates RTL-designbeskrivelsen inn i en syntesemotor, sammen med ytterligere designdetaljer, som FPGA-type, pinneoppgaver og tidsbegrensninger. Resultatet fra syntesemotoren er en konfigurasjonsfil som lastes inn i FPGA-en. (Bildekilde: Max Maxfield)

Efinix' Efinity IDE faller innunder denne verktøyklassen. Denne programvaren gir en komplett RTL-til-bitstream-flyt med et enkelt og brukervennlig grafisk brukergrensesnitt (GUI), samt støtte for kommandolinjeskripting. Et intuitivt instrumentbord veileder utvikleren gjennom flyten (dvs. syntese, plassering, føring, bitstream-generasjon), der hvert trinn kan styres automatisk eller manuelt. Utviklere kan bruke Efinitys syntesemotor til å utnytte Quantum-arkitekturen man finner i Trion FPGA-er for å generere enheter med fire ganger PPA-forbedringer.

I tillegg til å støtte simuleringsflyter ved bruk av ModelSim, NCSim eller gratis IVerilog-simuleringer, har Efinity IDE også et grensesnittdesign for å begrense logikken og tildele pinner til blokker i enhetens periferi, et redigeringsprogram for plantegninger hvor du kan bla gjennom designets logikk- og føringsplassering, en timingnettleser og analyse av statisk timing for å måle ytelsen til designet, samt integrert feilsøking av maskinvare med logikkanalysator og virtuelle I/O-feilsøkingskjerner.

Konklusjon

Etter hvert som utviklere utfører mer bilde-, AI- og ML-behandling med Edge, må de i stedet for, eller for å utfylle, en skybasert tilnærming anse FPGA-ene som en del av behandlingsarkitekturen for å håndtere problemer som kostnader, ytelse, strømforbruk, størrelse, skalerbarhet, fleksibilitet og oppgraderinger på en bedre måte.

For noen utviklere kan dette innebære en læringskurve, men med fremskrittene innen FPGA-er, som Efinix' Quantum-teknologi, kan denne investeringen fort bli verdt å ta på grunn av lavere kostnader, mindre formfaktorer, bedre ytelse og større fleksibilitet.

Som et resultat er FPGA-er nå ideelle for både tradisjonelle FPGA-programmer og fremvoksende Edge-databehandling for bruksområder innen mobil, IoT, automasjon, robotikk, sensorfusjon, datamaskinvisjon, AI og ML.

Ytterligere resurser

- Grunnleggende: IoT, IIoT, AIoT og hvorfor de er fremtidens industrielle automatisering

- Grunnleggende om FPGA-er: Hva er FPGA-er og hvorfor trenger vi dem?

- Grunnleggende om FPGA-er – Del 2: Komme i gang med Lattice Semiconductors FPGA-er

- Grunnleggende om FPGA-er – Del 3: Komme i gang med Microchip Technologys FPGA-er

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.