Hvorfor og hvordan du bruker Efinix FPGA-er for AI/ML-bilder Del 2: Bildefangst og -behandling

Bidrag fra DigiKey's European Editors

2023-05-05

Redaktørens merknad: Nye tilnærminger til FPGA-arkitekturer gir finere og større fleksibilitet for å møte behovene til maskinlæring (ML) og kunstig intelligens (AI, på norsk også kalt KI). Del 1 av denne todelte serien introduserer en slik arkitektur fra Efinix og hvordan man kommer i gang med den ved hjelp av et utviklingskort. Her tar vi for oss del 2 grensesnittet mellom utviklingskortet og eksterne enheter og periferiutstyr som et kamera, og hvordan man kan utnytte FPGA for å fjerne flaskehalser for bildebehandling.

FPGA-er spiller en kritisk rolle i mange programmer, fra industriell styring og sikkerhet til robotikk, luftfart og kjøretøyindustri/bilindustri. Takket være den fleksible naturen til den programmerbare logikkjernen og deres brede grensesnittfunksjoner, er en voksende brukstilfelle for FPGA-er i bildebehandling, hvor maskinlæring (ML) kan distribueres. FPGA-er er ideelle for implementering av løsninger som har flere høyhastighets kameragrensesnitt takket være deres parallelle logiske struktur. I tillegg gjør FPGAer det også mulig å bruke en dedikert prosesseringsrørledning i logikken, og dermed fjerne delte ressursflaskehalser som ville være forbundet med CPU- eller GPU-baserte løsninger.

Denne nærmere titten på Titanium-FPGA-er fra Efinix vil gå gjennom bildebehandlingsprogrammet for referansebilder som følger med FPGA-ens Ti180 M484-utviklingskort. Målet er å forstå designets bestanddeler, og å identifisere hvor FPGA-teknologien gjør det mulig å fjerne flaskehalser eller muliggjør andre fordeler for utviklere.

Ti180 M484-basert referansekonstruksjon

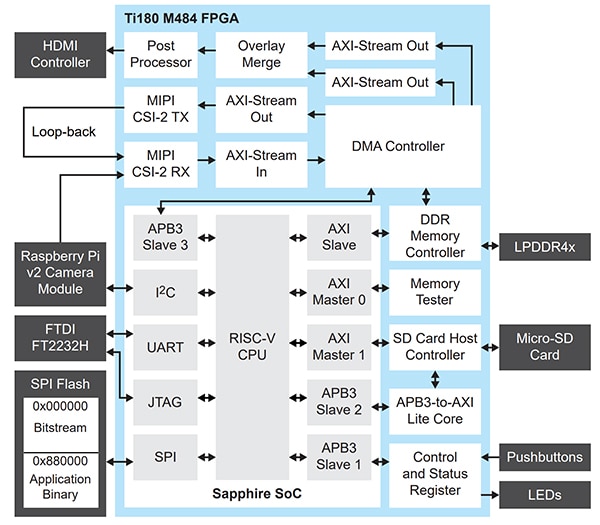

Konseptuelt mottar referansedesignen (figur 1) bilder fra flere MIPI-kameraer (Mobile Industry Processor Interface), utfører rammebuffring i LPDDR4x, og sender deretter ut bildene til en HDMI-skjerm (High Definition Multimedia Interface). Et FPGA mezzaninkort (FMC) og fire Samtec QSE-grensesnitt på kortet brukes til å levere kamerainngangene og HDMI-utgangen.

Bilde 1: Konseptuelt mottar Ti180 M484-referansedesignen bilder fra flere MIPI-kameraer, utfører rammebuffring i LPDDR4x, og sender deretter ut bildene til en HDMI-skjerm. >(Bildekilde: Efinix)

Bilde 1: Konseptuelt mottar Ti180 M484-referansedesignen bilder fra flere MIPI-kameraer, utfører rammebuffring i LPDDR4x, og sender deretter ut bildene til en HDMI-skjerm. >(Bildekilde: Efinix)

FMC til QSE-ekspansjonskortet brukes sammen med HDMI-datterkortet for å gi utgangsvideobanen, mens tre QSE-kontakter brukes til grensesnitt med DFRobot SEN0494 MIPI-kameraene. Hvis flere MIPI-kameraer ikke er tilgjengelige, kan et enkelt kamera brukes ved å sløyfe tilbake den enkelte kamerakanalen for å simulere flere kameraer.

På et høyt nivå kan denne programet synes å være enkel. Det er imidlertid utfordrende å motta flere HD MIPI-datastrømmer med høy bildefrekvens. Det er her FPGA-teknologien er gunstig fordi den lar designere bruke flere MIPI-datastrømmer parallelt.

Referansedesignets arkitektur utnytter både parallelle og sekvensielle behandlingsstrukturer med FPGA. De parallelle strukturer brukes til å implementere bildebehandlingsrørledningen, mens en RISC-V-prosessor leverer den sekvensielle prosessering som brukes for FPGA-oppslagstabellene (LUT).

Bildebehandlingsrørledningen kan deles i to elementer i mange FPGA-baserte bildebehandlingssystemer, nemlig inngangs- og utgangsdatastrømmene. Inngangsdatastrømmen er koblet til kamera/sensor-grensesnittet, og prosesseringsfunksjoner brukes på sensorens utgang. Disse funksjonene kan inkludere Bayer-konvertering, automatisk hvitbalanse og andre forbedringer. I utdatastrømmen er bildet klargjort for visning. Dette inkluderer endring av fargerom (f.eks. RGB til YUV) og etterbehandling for ønsket utgangsformat, slik som HDMI.

Ofte opererer inngangsbildets prosesseringskjede ved sensorpikselens klokkehastighet. Dette har forskjellig timing til utgangskjeden, som behandles ved utgangsfrekvensen.

En rammebuffer brukes til å koble inngangen til utgangsbehandlingsrørledningen, som ofte lagres i eksternt høyytelsesminne, for eksempel LPDDR4x. Denne rammebufferen frakobles mellom inngangs- og utgangsrørledningene, noe som tillater tilgang til rammebufferen via direkte lageraksess ved den passende klokkefrekvensen.

Ti180-referansedesign bruker en lignende tilnærming til konseptene som er skissert ovenfor. Inngangsbildebehandlingsrørledningen implementerer en MIPI Camera Serial Interface 2 (CSI-2) mottaker intellektuell eiendom-kjerne (IP-kjerne), som er bygget på MIPI fysiske lag (MIPI D-PHY) -kapabelinngang/utgang (I/O) av Titanium FPGA. MIPI er et utfordrende grensesnitt fordi det bruker både single-ended og differensialsignalering på samme differensialpar, i tillegg til lavhastighets- og høyhastighetskommunikasjon. Integrering av MIPI D-PHY i FPGA I/O reduserer kompleksiteten av kretskortdesignen, samtidig som materialregningen (bom) reduseres.

Med bildestrømmen fra kameraet mottatt, konverterer referansedesignet deretter utgangen til MIPI CSI-2 RX til en avansert eXtensible Interface (AXI)-datastrøm. En AXI-datastrøm er et ensrettet høyhastighetsgrensesnitt som gir en strøm av data fra en master til en slave. Håndtrykksignaler for overføring mellom en master og en slave er leverte (tvalid og tready) sammen med sidebåndsignaler. Disse sidebåndsignalene kan brukes til å formidle informasjon om bildetiming, slik som start av ramme og ende av linje.

AXI-datastrøm er ideell for bildebehandlingsprogrammer og gjør det mulig for Efinix å gi en rekke bildebehandlings-IP som deretter enkelt kan integreres i prosesseringskjeden som kreves av programmet.

Etter å ha blitt mottatt blir MIPI CSI-2-bildedataene og tidssignalene omformet til en AXI-strøm og innmatet til en DMA-modul (direct memory access), som skriver bilderammen til LPDDR4x og virker som rammebuffer.

Denne DMA-modulen opererer under kontroll av RISC-V-kjernen i FPGA i et Sapphire-systemkrets (SoC). Denne systemkretsen (SoC-en) tilveiebringer styring, slik som å stoppe og starte DMA-skriving, i tillegg til å forsyne DMA-skrivekanalen med den nødvendige informasjon for korrekt å skrive bildedataene til LPDDR4x. Dette inkluderer informasjon om minneplassen og bredden og høyden på bildet definert i byte.

Utgangskanalen i referansedesignen leser bildeinformasjonen fra LPDDR4x-rammebufferen under styring av RISC-V-systemkretsen (SoC-en). Dataene blir sendt ut fra DMA IP som en AXI-datastrøm, som deretter blir konvertert fra RAW-format forsynt fra sensoren til RGB-format (figur 2), og klargjort for utgang over den innebygde Analog Devices ’ADV7511 HDMI-sender.

Bilde 2: Eksempelbilder utgang fra referansedesignen. (Bildekilde: Adam Taylor)

Bilde 2: Eksempelbilder utgang fra referansedesignen. (Bildekilde: Adam Taylor)

Bruken av DMA gjør det også mulig for Sapphire-systemkretsen (SoC-en) RISC-V å få tilgang til bildene som er lagret i rammebufferen, og den abstrakte statistikken og bildeinformasjonen. Sapphire-systemkretsen (SoC-en) er også i stand til å skrive overlegg inn i LPDDR4x slik at de kan slås sammen med utdatastrømmen av video.

Moderne CMOS-bildesensorer (CIS) har flere driftsmoduser og kan konfigureres til å gi prosessering på brikken (systemkretsen), samt flere forskjellige utdataformater og klokkesystemer. Denne konfigurasjon forsynes normalt over et I² C-grensesnitt. I Efinix referansedesign er denne I²C-kommunikasjonen til MIPI-kameraene forsynt fra Sapphire-systemkretsen (SoC-en) RISC-V-prosessoren.

Integrasjon av RISC-V-prosessoren i Titanium FPGA reduserer den totale størrelsen på den endelige løsningen, da det fjerner behovet for å implementere både komplekse FPGA-tilstandsmaskiner som øker designrisikoen, samt eksterne prosessorer som legger til stykklisten.

Inkludering av prosessoren muliggjør også støtte med ekstra IP for å kommunisere med MicroSD-kortet. Dette gjør det mulig for virkelige programmer der bilder kan være nødvendig å bli lagret for senere analyse.

Samlet sett er arkitekturen til Ti180-referansedesign optimalisert for å muliggjøre en kompakt, rimelig, men likevel høyytelsesløsning som gjør det mulig for utviklere å redusere materialkostnader i forbindelse med systemintegrasjon.

En av de viktigste fordelene med referansedesign er at de kan brukes til å kickstarte programutvikling på tilpasset maskinvare, slik at utviklere kan ta kritiske elementer i designet og bygge av det med sine nødvendige tilpasninger. Dette inkluderer muligheten til å bruke Efinixs TinyML-flyt til å implementere visjonsbaserte TinyML-programmer som kjører på FPGA. Dette kan utnytte både FPGA-logikkens parallelle natur og muligheten til enkelt å legge til tilpassede instruksjoner i RISC-V-prosessorer, slik at det kan opprettes akseleratorer i FPGA-logikken.

Implementering

Som diskutert i del 1, er Efinix-arkitekturen unik ved at den bruker XLR-celler (eXchangeable Logic and Routing-celler) for å gi både ruting og logisk funksjonalitet. Et videosystem slik som referansekonstruksjonen er et blandet system som er både logisk og rutingstungt: omfattende logikk er nødvendig for å implementere bildebehandlingsfunksjonene, og omfattende ruting er nødvendig for å forbinde IP-cellene ved de nødvendige frekvenser.

Referansedesignet bruker omtrent 42 % av XLR-cellene i enheten, noe som gir god plass for tillegg, inkludert tilpassede programmer som edge-ML (inngangspunkt-ML).

Bruken av blokk-RAM og digitale signalbehandlingsblokker (DSP) er også svært effektiv, ved å bruke bare 4 av de 640 DSP-blokkene og 40% av minneblokkene (figur 3).

|

Figur 3: Ressurstildeling på Efinix-arkitekturen viser at bare 42 % av XLR-cellene brukes, noe som gir god plass til ytterligere prosesser. (Bildekilde: Adam Taylor)

Ved anordningen IO brukes DDR-grensesnittet for LPDDR4x til å levere program-minnet for Sapphire-systemkretsen (SoC-en) og bilderammebufferne. Alle de innretningstilpassede MIPI-ressursene utnyttes sammen med 50 % av faselåssløyfene (figur 4).

|

Bilde 4: Snapshot av grensesnittet og I/O-ressurser som brukes. (Bildekilde: Adam Taylor)

Det generelle formålet I/O (GPIO) brukes til å levere I2C-kommunikasjon sammen med flere av grensesnittene som er koblet til Sapphire-systemkretsen (SoC-en), inkludert NOR FLASH, USB UART og SD-kort. HSIO brukes til å gi høyhastighets videoutgang til ADC7511 HDMI-senderen.

Et av de avgjørende elementene når man designer med FPGA-er, er ikke bare å implementere og montere designen i FPGA-en, men også å kunne plassere logikkdesignen i FPGA-en og oppnå den nødvendige tidsstyringsytelsen når den dirigeres.

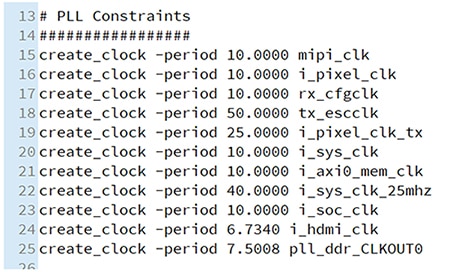

Tiden med FPGA-design med ett klokkedomene er forbi, for lenge siden. Det er flere forskjellige klokker, alle kjører på høye frekvenser i Ti180 referanse design. Den endelige tidstabellen viser de maksimale frekvensene som oppnås for klokkene i systemet. Det er her den forespurte tidsstyringsytelsen også kan ses i begrensningene (figur 5), som har en maksimal klokkefrekvens på 148,5 megahertz (MHz) for HDMI-utgangsklokken.

Bilde 5: Klokkebegrensninger for referansedesignet. (Bildekilde: Adam Taylor)

Bilde 5: Klokkebegrensninger for referansedesignet. (Bildekilde: Adam Taylor)

Tidsbestemt implementering mot begrensningene viser potensialet til Titanium FPGA XLR-strukturen da den reduserer den mulige ruteforsinkelsen, og dermed øker designytelsen (figur 6).

|

BildeFigur 6: Tidsbestemt implementering mot begrensningene viser potensialet til Titanium FPGA XLR-strukturen for å redusere den mulige ruteforsinkelsen, og dermed øke designytelsen. (Bildekilde: Adam Taylor)

Konklusjon

Ti180 M484-referansedesignen viser klart mulighetene til Efinix FPGA-er og Ti180 spesielt. Utformingen utnytter flere av de unike I/O-strukturene for å implementere en kompleks bildebehandlingsbane som støtter flere innkommende MIPI-datastrømmer. Dette bildebehandlingssystemet opererer under kontroll av en myk kjerne Sapphire-systemkretsen (SoC-en), som implementerer programmets nødvendige sekvensielle behandlingselementer.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.