Forstå og minimer virkningen av jitter på høyhastighetskoblinger

Bidrag fra DigiKeys nordamerikanske redaktører

2023-12-21

Klokkeoscillatorer gir taktpulsen til moderne kretser ved temporegulerisng systemkomponenter. Når systemhastighetene øker til hundrevis av megahertz (MHz) og høyere, må disse klokkene være raskere og gi svært lav jitter, vanligvis under 100 femtosekunder (fs), for å opprettholde systemytelsen. De må også opprettholde sine lave jitterspesifikasjoner over tid, til tross for variasjoner i temperatur og spenning.

Noe jitter induseres av signalbanestøy og forvrengning, og det kan reduseres noe ved å bruke omklokkins- og retimingsteknikker. Imidlertid genereres jitter også av klokkekilden, som vanligvis er en oscillator. Dette skyldes forskjellige fysiske fenomener, inkludert termisk støy, prosessfeil, strømforsyningsstøy, annen ekstern støy som kommer inn i klokkeoscillatoren, materialpåkjenninger og mange andre subtile faktorer. Uavhengig av kilden er det opp til designeren å gjøre alt for å minimere iboende klokkejitter, da manglene ikke er reversible.

Denne artikkelen diskuterer jitterproblemer fra ulike perspektiver. Den introduserer deretter forskjellige klokkeoscillatorer fra Abracon LLC og viser hvordan jitter kan minimeres ved å tilpasse klokkeoscillatorens ytelse til utrustningen.

Grunnleggende om jitter

Klokkejitter er avviket til en klokkekant fra dens ideelle posisjon i tid. Denne jitteren påvirker timingpresisjonen og nøyaktigheten til overføringen av datasignaler som klokkesignalet pacer, noe som fører til degradering av signal-til-støy-forholdet (SNR) i mottakerens dekodings-/demodulasjonskretser eller andre system-IC-er. Dette resulterer i en høyere bitfeilrate (bit error rate – BER), økte reoverføringer og redusert effektiv datagjennomstrømning.

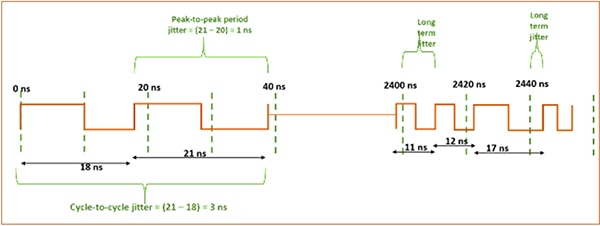

Gitt dens kritikkverdighet, analyseres klokkejitter mye i systemer som sender et signal fra en sendekilde til en mottaker over kabler, kontakter eller kretskort. Avhengig av utrustningen kan den karakteriseres på mange måter, inkludert syklus-til-syklus, periode og langsiktig jitter (Figur 1).

Figur 1: Begrepet «jitter» omfatter mange tidsvariasjoner, inkludert syklus-til-syklus-jitter, periode-jitter og langsiktig jitter. (Bildekilde: VLSI Universe)

Figur 1: Begrepet «jitter» omfatter mange tidsvariasjoner, inkludert syklus-til-syklus-jitter, periode-jitter og langsiktig jitter. (Bildekilde: VLSI Universe)

- Syklus-til-syklus-jitter betegner endringen i klokkeperiode over to påfølgende sykluser og er ikke relatert til frekvensvariasjon over tid.

- Periodejitter er avviket til en hvilken som helst klokkeperiode i forhold til dens middelperiode. Det er forskjellen mellom den ideelle og faktiske klokkeperioden, og kan spesifiseres som enten rot-mean-square (RMS) periode-jitter eller topp-til-topp periode-jitter.

- Langvarig jitter er klokkekantens avvik fra sin ideelle posisjon over lengre tid. Det kan sammenlignes med avvik/drift.

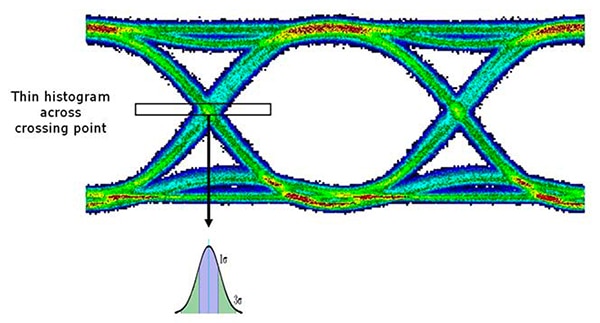

Jitter kan ødelegge timingen som brukes av andre underfunksjoner, komponenter eller systemer som brukes for å oppnå lav BER-datagjenoppretting, eller tempokomponenter som minneelementer eller prosessorer i et synkront system. Det vises i øyediagrammet i figur 2 som en utvidelse av krysningspunktet i timingen av bits.

Figur 2: I et øyediagram blir jitter sett på som en utvidelse av det kritiske tidskrysspunktet i datastrømmen. (Bildekilde: Kevin K. Gifford/Univ. i Colorado)

Figur 2: I et øyediagram blir jitter sett på som en utvidelse av det kritiske tidskrysspunktet i datastrømmen. (Bildekilde: Kevin K. Gifford/Univ. i Colorado)

For serielle datakoblinger må kretsene i mottakerenden forsøke å gjenopprette sin egen klokke for optimal datastrømdekoding. For å gjøre dette må den synkroniseres og låses til kildeklokken, ofte ved hjelp av en faselåsesløyfe (PLL). Jitter påvirker systemets evne til å gjøre dette nøyaktig, og kompromitterer dets evne til å gjenopprette dataene med en lav BER.

Merk at jitter kan måles i både tids- og frekvensdomenene; begge er like gyldige perspektiver på det samme fenomenet. Fasestøy er et frekvensdomenebilde av støyspekteret rundt oscillatorsignalet, mens jitter er et tidsdomenemål for tidsnøyaktigheten til oscillatorperioden.

Jittermålinger kan uttrykkes på flere måter. Det er ofte sitert ved bruk av tidsenheter som "jitter på 10 picosekunder" (ps). Root mean square (RMS) fasejitter er en tidsdomeneparameter som er utledet fra fasestøymålingen (frekvensdomene). Jitter blir noen ganger også referert til som fasejitter som kan være forvirrende, men det er fortsatt tidsdomenejitter-parameteren.

Ettersom koblingsdriftsfrekvensene og klokkene deres øker fra noen få titalls MHz til hundrevis av MHz og høyere, reduseres den tillatte jitteren på klokkekilden til rundt 100 fs eller mindre. Disse frekvensene gjelder for optiske moduler, cloud computing, nettverk og høyhastighets Ethernet, som alle er funksjoner og utrustningen som krever en bærefrekvens mellom 100 og 212/215 MHz og datahastigheter på opptil 400 gigabit per sekund (Gbps).

Håndtering av krystallen

Den vanligste måten å skape et stabilt, konsistent, nøyaktig-frekvens klokkesignal er å bruke en kvartskrystalloscillator. En tilknyttet oscillatorkrets støtter krystallen. Det er mange slike kretsfamilier, hver med forskjellige fordeler og bakdeler. Krystaller har blitt brukt i denne rollen siden 1930-tallet for trådløs radiokommunikasjon i mellomfrekvente (300 kilohertz (kHz) til 3 MHz) og høyfrekvente (3 til 30 MHz) RF-bånd.

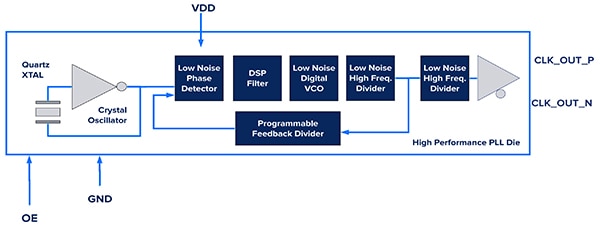

En mye brukt tilnærming for å generere klokker med lav jitter er å bruke en av de mange variasjonene på PLL-baserte arkitekturer. For eksempel kommer enheter i Abracons AX5- og AX7 ClearClock™-familier i kapslinger på henholdsvis 5 × 3,2 mm og 5 × 7 mm, samt de bruker en sofistikert PLL-teknologi for overlegen ytelse med lav jitter (Figur 3).

Figur 3: Abracon AX5 og AX7 klokkeoscillatorene bruker en av de mange PLL-baserte designene, men med subtile forbedringer for å minimere jitter. (Bildekilde: Abracon)

Figur 3: Abracon AX5 og AX7 klokkeoscillatorene bruker en av de mange PLL-baserte designene, men med subtile forbedringer for å minimere jitter. (Bildekilde: Abracon)

Sammen med driftsfrekvens og oscillatordesign, påvirkes jitter-ytelsen av den fysiske størrelsen på kvartskrystallen ved oscillatorkjernen. Ettersom størrelsen på denne krystallen reduseres, blir det mer utfordrende å gi overlegen RMS-jitter-ytelse.

For klokkeløsninger i 100 til 200 MHz-båndet, og i mindre formfaktorer enn de PLL-baserte AX5- og AX7-enhetene, er det behov for en ny oscillatorarkitektur. Disse kravene for mindre størrelser er vanligvis knyttet til den nyeste generasjonen optiske transceivere og moduler. Det er fire etablerte måter å designe en klokkeoscillator i området 100 til 200 MHz:

- Bruk en kvartsoscillator med en invertert mesa-kvarts som resonatorelement

- Bruk en kvartsoscillator med et kvartsemne med tredje overtone som resonatorelement

- Bruk en oscillatorsløyfe basert på en sub-50 MHz, tredje overtone/fundamental-modus kvartsblank, eller en sub-50 MHz, temperaturkompensert krystalloscillator parret med en heltalls- eller fraksjonsmodus PLL–IC

- Bruk en sub-50 MHz mikroelektromekanisk system (MEMS) resonatorbasert oscillatorsløyfe parret med en heltalls- eller fraksjonsmodus PLL-IC

Alternativ 1 tilbyr ikke den beste RMS-jitter-ytelsen, og det er heller ikke den mest kostnadseffektive løsningen. Alternativ 3 blir komplisert og har ytelsesmangler, mens MEMS-resonatortilnærmingen til alternativ 4 ikke oppfyller de primære ytelseskriteriene på 200 fs maksimal RMS-jitter. I motsetning til dette bruker alternativ 2 et optimalt utformet tredje overtonet kvartsemne med hensyn til geometrien til elektrodene og optimaliseringen av kuttevinkelen. Denne kombinasjonen er optimal når det gjelder kostnader, ytelse og størrelse.

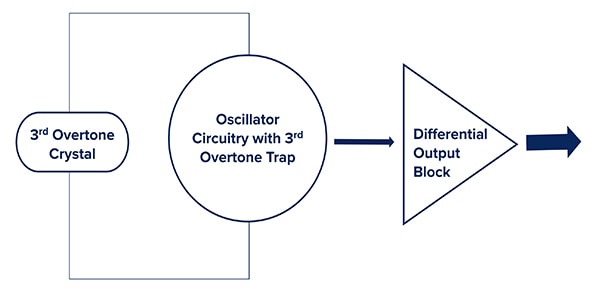

Ved hjelp av denne tilnærmingen utviklet Abracon ClearClock-løsninger med «tredje overtone» (figur 4). Disse enhetene bruker en mer stillegående arkitektur for å muliggjøre overlegen, ultralav RMS-jitter-ytelse og ekstrem energieffektivitet i miniatyrkapslinter så små som 2,5 × 2,0 x 1,0 mm.

Figur 4: Den «tredje overtonen»-ClearClock-løsningen fra Abracon bruker en mer stillegående arkitektur for å forbedre den generelle ytelsen og energieffektiviteten. (Bildekilde: Abracon)

Figur 4: Den «tredje overtonen»-ClearClock-løsningen fra Abracon bruker en mer stillegående arkitektur for å forbedre den generelle ytelsen og energieffektiviteten. (Bildekilde: Abracon)

I dette opplegget sikrer forsiktig utforming av tredje overtonens krystalloverflate, sammen med riktig filtrering og «fanging» av det ønskede bæresignalet, enestående RMS-jitter-ytelse ved de ønskede bærefrekvensene.

Denne arkitekturen bruker ikke en typisk PLL-tilnærming, så det er ingen oppkonvertering. Følgelig er det ikke behov for standard PLL-brøk- eller heltallsmultiplikasjon, og den endelige utgangsfrekvensen har en en-til-en korrelasjon med resonansfrekvensen til den tredje overtone kvartskrystallen. Fraværet av brøk- eller heltallsmultiplikasjon forenkler designet og muliggjør minimalt jitter i minste mulige størrelse.

Spesifikasjoner og ytelse i virkeligheten

Klokkeoscillatorer er mer enn bare en krystall og dens analoge krets. De inkluderer bufring for å sikre at oscillatorens utgangsbelastning og dens kortsiktige og langsiktige variasjoner ikke påvirker enhetens ytelse. De støtter også forskjellige differensielle digitale logiske utgangsnivåer for kretskompatibilitet. Denne kompatibiliteten fjerner behovet for en ekstern oversettelses-IC på logikknivå. En slik IC vil øke kostnadene, fotavtrykket og jitter.

Ettersom klokkeoscillatorer brukes i så mange forskjellige utrustninger med forskjellige spenningsområder (rail voltages), må de tilbys i en rekke forsyningsspenninger som +1,8 volt, +2,5 volt eller +3,3 volt, samt egendefinerte verdier som vanligvis spenner fra 2,25 til 3,63 volt. De må også være tilgjengelige med forskjellige utdataformatalternativer som lavspennings positiv/pseudo emitter-koblet logikk (LVPECL) og lavspennings differensialsignalisering (LVDS), samt andre formater.

En titt på to familier av krystallklokkeoscillatorer, AK2A og AK3A, viser hva som kan oppnås gjennom sofistikert forståelse og integrering av materialer, konstruksjon, arkitektur og test. De to familiene har mange likheter, de viktigste forskjellene er størrelse og maksimal frekvens.

Familien AK2A: Denne familien av krystalloscillatorer tilbys ved nominelle frekvenser fra 100 til 200 MHz og er tilgjengelig med driftsspenninger på 2,5 volt, 3,3 volt og 2,25 til 3,63 volt med LVPECL-, LVDS- og HCSL-differensialutgangslogikk.

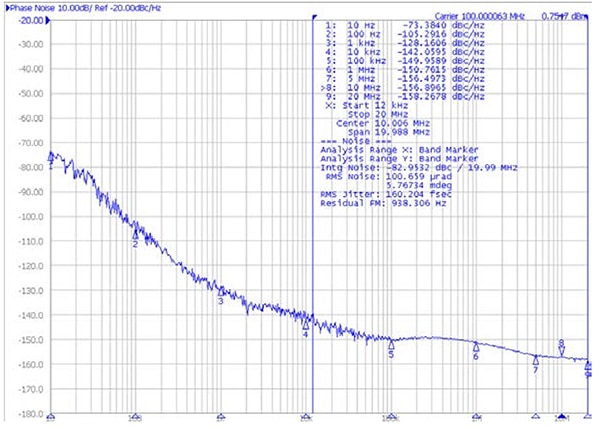

Alle familiemedlemmer har lignende ytelse, inkludert lav RMS-jitter. For eksempel AK2ADDF1-100.000T er en enhet med 100,00 MHz, 3,3 volt og LVDS-utganger, samt en RMS-jitter på 160,2 fs (Figur 5). Frekvensstabiliteten er utmerket ved bedre enn ±15 deler per million (ppm) over temperatur, og den kommer i en seks-avledet, overflatemontert enhet (SMD-kapsling) som måler 2,5 × 2 × 1 mm.

Figur 5: Jitter er vist å være 160 fs for AK2ADDF1-100.000T, en 3,3 volt, 100 MHz enhet med LVDS-utganger. (Bildekilde: Abracon)

Figur 5: Jitter er vist å være 160 fs for AK2ADDF1-100.000T, en 3,3 volt, 100 MHz enhet med LVDS-utganger. (Bildekilde: Abracon)

Når klokkefrekvensene øker, må imidlertid jitter reduseres for å opprettholde ytelsen på systemnivå. For AK2ADDF1-156.2500T, en 156,25 MHz LVDS-oscillator, faller den typiske RMS-jitteren til 83 fs.

Familien AK3A: Enheter i AK3A-familien er litt større enn de i AK2A-familien med et fotavtrykk på 3,2 × 2,5 × 1 mm (figur 6). Versjoner spesifisert til 212,5 Mhz er tilgjengelige, noe høyere enn 200 MHz-grensen for AK2A-familien.

Figur 6: AK3A-krystalloscillatorene (høyre) er litt lengre og bredere enn AK2A-serien (venstre); versjoner er tilgjengelige for frekvenser på opptil 212,5 MHz, sammenlignet med 200 MHz for AK2A. (Bildekilde: Abracon)

Figur 6: AK3A-krystalloscillatorene (høyre) er litt lengre og bredere enn AK2A-serien (venstre); versjoner er tilgjengelige for frekvenser på opptil 212,5 MHz, sammenlignet med 200 MHz for AK2A. (Bildekilde: Abracon)

Generelle spesifikasjoner for denne AK3A-enheten er lik de til det tilsvarende AK2A-familiemedlemmet. Et eksempel er AK3ADDF1-156.2500T3, en 156,25 MHz LVDS-oscillator som har en typisk RMS-jitter på 81 fs, noe bedre enn det tilsvarende medlemmet av AK2A-familien.

Jitter for begge familier varierer avhengig av driftsfrekvens, driftsspenning, kapslingsstørrelse og valg av utganger.

Tilleggsbetraktninger fra den virkelige verden

Det er ikke nok å ha en klokkeoscillator som bare fungerer i henhold til spesifikasjonene den dagen den forlater fabrikken. Som med alle komponenter, spesielt analoge og passive komponenter, er disse oscillatorene utsatt for avvik/drift over tid på grunn av aldring av de inngående materialene og indre spenninger.

Denne virkeligheten er spesielt utfordrende for høyytelses klokkeoscillatorer, da det ikke er noen praktiske eller enkle måter å korrigere eller kompensere for avviket/driften ved å legge til programvare eller smarte kretser. Det er imidlertid noen måter å redusere avvik/drift av drift på. Disse inkluderer lange perioder med innbrenning for sluttbrukeren, dette for akselerert oscillatoraldring, alternativt bruk av en temperaturstabilisert oscillator i et termostabilisert kabinett. Førstnevnte er tidkrevende og en forsyningskjedeutfordring, mens sistnevnte er stor, kostbar og strømkrevende.

Abracons ClearClock-familie anerkjenner at aldring er en kritisk parameter, og tilbyr en streng, altomfattende frekvensnøyaktighet over hele sluttproduktets levetid på 10 til 20 år. Abracon sikrer samsvar med frekvensstabilitet på bedre enn ±50 ppm i denne perioden. Dette oppnås ved nøye valg og fabrikasjon av den tredje overtonekrystallet og kondisjonering for å oppfylle ±15 ppm stabilitet over -20 °C til + 70 °C og ±25 ppm stabilitet over -40 °C til + 85 °C.

Som alltid handler teknikk om kompromisser. Abracon AK2A- og AK3A-seriene gir forbedret jitter-støyytelse sammenlignet med forgjengerseriene (henholdsvis Gen I AK2 og AX3) ved å bruke en neste generasjons (Gen II) oscillator ASIC, og dermed sikre ultralav RMS-jitterytelse.

Denne forbedringen oppnås på bekostning av en liten økning i strømforbruket. Det maksimale strømforbruket øker fra 50 milliampere (mA) for Gen I til 60 mA for Gen II, selv om lavspenningsenhetene kjører omtrent halvparten av denne verdien. Andregenerasjons ClearClock-oscillatorene gir derfor ultralav RMS-jitter samtidig som de opprettholder lavt strømforbruk.

Konklusjon

Timing-oscillatorer er hjerterytmen til en datalink eller klokkefunksjon, og deres nøyaktighet, jitter og stabilitet er kritiske parametere for å oppnå den nødvendige ytelsen på systemnivå, inkludert høy SNR og lav BER. Høyere klokkefrekvenser kan oppnås med nyskapende materialvalg og arkitekturer som oppfyller de strenge ytelsesspesifikasjonene som kreves av bransjen og dens ulike standarder. Abracon AK2A- og AK3A-serien har jitter under 100 fs i området 100 til 200 MHz i kapslinger for overflatemontering (SMD-kapslinger) som kun måler noen få millimeter på hver side.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.