Lag raskt høyfrekvente klokker med lav jitter ved hjelp av en translasjonsløkke-modul

Bidrag fra DigiKeys nordamerikanske redaktører

2021-08-04

Konstruktører av instrumenterings- og målesystemer krever signaler med lav jitter, som ikke er falske, for å gi signal-til-støy-forhold (signal-to-noise ratios – SNR) eller feilvektorstørrelser (error vector magnitudes – EVM) som kreves for å oppfylle stadig mer krevende kundekrav. Samtidig står de også overfor et betydelig press for å redusere fysisk størrelse på kretskort, samt designkostnader og kompleksitet. Sistnevnte er avgjørende i forhold til å korte ned utviklingstiden for forkorte tiden det tar å få ferdig produkt ut på markedet.

For å takle de mange utfordringene med utrustning, må ingeniører omstille sine instrumenterings- og måleklokkeløsninger fra skreddersydde tradisjonelt frittstående (diskrete) konstruksjoner til mer integrerte løsninger. Et viktig skritt mot dette er å bruke en integrert translasjons-fasereguleringssløyfe (phase-lock-loop – PLL). Dette tillater frekvensoppbygging av et tradisjonelt spenningsstyrt oscillatorsignal (VCO-signal), samtidig som jitteren og fasestøyen fra en fast ekstern lokal oscillator (LO) i det vesentlige opprettholdes.

Denne artikkelen tar for seg rollen til translasjonsløkker for å oppnå bransjens laveste integrerte fasestøy. For eksempel introduserer denADF4401A translation loop system-in-package (TL SiP) fraAnaloge enheter og viser hvordan den ivaretar ytelseskrav gjennom et utgangssignal med sub-10 femtosekund (fs) rms bredbånds integrert jitterkapasitet og forbedret isolasjon for å dempe falske komponenter, samtidig som de oppfyller designernes integrasjon, kostnader, kompleksitet og time-to-market behov .

Tradisjonell PLL kontra translasjonsløkke-operasjoner

Hovedformålet med en translasjonsløkke er å generere et utgangssignal som er låst til et inngangsreferansesignal med betydelig redusert fasestøy innenfor båndet, sammenlignet med tradisjonelle PLL-er.

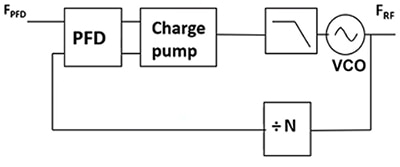

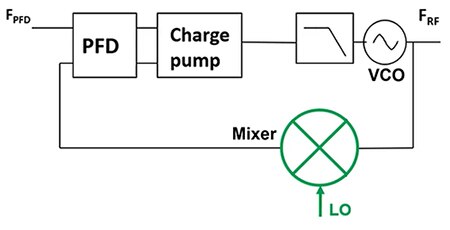

En standard PLL består av et tilbakemeldingssystem som inneholder en fasefrekvensdetektor (PFD), ladepumpe, lavpassfilter (LPF), VCO og en frekvensdeler med tilbakemelding N (figur 1).

Figur 1: Standard PLL låses til en referanse med lavere frekvens (FPFD) og genererer en utgangsfrekvens (FRF). (Bildekilde: Bonnie Baker)

Figur 1: Standard PLL låses til en referanse med lavere frekvens (FPFD) og genererer en utgangsfrekvens (FRF). (Bildekilde: Bonnie Baker)

PFD-en sammenligner fasen av inngangsreferansen og fasen av tilbakemeldingssignalet og genererer en serie pulser proporsjonalt med fasefeilen mellom dem. Ladepumpen mottar PFD-pulser og konverterer dem til strømkilde eller synkepulser som i sin tur vil stille VCO-en enten opp eller ned i frekvens. LPF fjerner alle pulsenes høyfrekvente energi og konverterer dem til en spenning som VCO-en kan bruke. VCO-ens utgangssignal mates tilbake til PFD-blokken gjennom N-deleren for å fullføre sløyfen.

Figur 1: Frekvensoverføringsfunksjonen beregnes ved hjelp av ligning 1:

![]() Ligning 1

Ligning 1

Der FRF er utgangsfrekvensen

N er tilbakekoblingsdelerforholdet (kan være heltall (integer) eller brøkdel)

FPFD er PFD-frekvensen

Figur 1 sitt gulv i støy innenfor båndet beregnes ved hjelp av ligning 2:

![]() Ligning 2

Ligning 2

Der FOMPLL er PLL sitt kvalitetstall (figure of merit – FOM) for gulvet i båndet

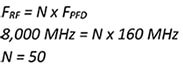

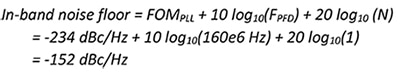

Tenk på et eksempel med et in FOM for gulvet innenfor båndet på -234 desibel per Hertz (dB/Hz); en PFD-frekvens (FPFD) på 160 megahertz (MHz) og en utgangsfrekvens (FRF) på 8 gigahertz (GHz).

For dette systemet brukes ligning 1 til å beregne verdien av N:

Ligning 2 brukes til å beregne støygulvet i båndet:

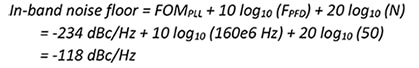

I beregningen ovenfor bidrar N-deleren sterkt til det samlede støygulvet i båndet, med 20 log10 (50), som tilsvarer 34 dB. En mindre N-verdi vil redusere støygulvet i båndet, men det vil også redusere utgangsfrekvensen. Så hvordan genererer vi en høy utgangsfrekvens og holder en lavere sløyfeforsterkning (N)?

Figur 2: For en standard PLL i dette eksempelet har støyen fra tilbakemeldingsdeleren (20 log10(N)) en 34 dB høyere støy innenfor båndet, sammenlignet med det nedre gule plottet, der er N = 1. (Bildekilde: Bonnie Baker)

Figur 2: For en standard PLL i dette eksempelet har støyen fra tilbakemeldingsdeleren (20 log10(N)) en 34 dB høyere støy innenfor båndet, sammenlignet med det nedre gule plottet, der er N = 1. (Bildekilde: Bonnie Baker)

Løsningen på dette problemet er å erstatte N-deleren med et nedkonverterende blandetrinn (figur 3).

Figur 3: En oversettelsessløyfe bruker en mikser for å nedkonvertere VCO-frekvensen til PFD-frekvensen i stedet for å bruke en tradisjonell tilbakemeldingsdeler. (Bildekilde: Bonnie Baker)

Figur 3: En oversettelsessløyfe bruker en mikser for å nedkonvertere VCO-frekvensen til PFD-frekvensen i stedet for å bruke en tradisjonell tilbakemeldingsdeler. (Bildekilde: Bonnie Baker)

I figur 3 erstatter mikseren tilbakemelding N-deleren, noe som resulterer i en sløyfeforsterkning lik 1 (N=1). Denne operasjonen vil i stor grad redusere bidraget fra tilbakemeldingssløyfen til støygulvet i båndet. For støyberegning innenfor båndet, er verdien av N nå lik 1. Ved hjelp av ligning 2 er støygulvet i båndet for det modifiserte systemet som følger:

Den nye støyen innenfor båndet viser en forbedring på 34 dBc/Hz.

I figur 3 er mikseren avhengig av en LO med ekstremt lav støy, kalt forskjøvet LO (Offset-LO). FLO ± FRF må være lik FPFD for å oppnå lås.

Med translasjonsløkkearkitekturen er fasestøyen til den forskjøvede LO-en svært viktig for å oppnå den beste ytelsen på RF-utgangen. På grunn av dette vil ingeniører vanligvis designe en forskjøvet LO (Offset-LO) basert på spenningsstyrt akustisk overflatebølge (surface acoustic wave – SAW), oscillatorer (VCSO-er), kamgeneratorer eller dielektriske resonatoroscillatorer (dielectric resonator oscillators – DRO-er). MERK: Kontakt Analog Devices for støtte med å designe Offset LO-er.

Utfordringer med translasjonsløkker

Tradisjonelt vil design som oppnår en støysvak translasjonsløkke behøve implementering av mange kretsblokker, noe som resulterer i design av en kompleks konstruksjon – stor i størrelse med begrenset fleksibilitet. I tillegg må hele kretsen valideres og karakteriseres for måloperasjonen. Et viktig konstruksjonsproblem er for eksempel LO-lekkasje (LO til RF-isolasjon) til RF-utgangssignalet. Dette er en betydelig utfordring for ingeniører å løse. Med tradisjonelle konstruksjoner, går ingeniører vanligvis videre til flere designiterasjoner for å oppnå optimalisert ytelse og egnet isolasjon.

Figur 3 viser hvordan ADF4401A integrerer hovedkretsblokker for å gi en fullstendig karakterisert løsning og eliminerer de tradisjonelt vanskelige områdene relatert til ytelse og isolasjon i translasjonsløkke-design. Denne programmerbare løsningen lar ingeniører oppnå optimalisert ytelse på første innsats og redusere tiden til markedet.

Evaluering av ADF4401A

ADF4401A er utviklet for å hjelpe ingeniører med å redusere tiden det tar å få produktet ut på markedet (time to market) for instrumentering med høy ytelse, ved hjelp av en frekvensgenereringsløsning med en RF-båndbredde på 62,5 MHz til 8 GHz. Ved å bruke en nedkonverterende mikser, har ADF4401A svært lav støy innenfor båndet, med en bredbånds jitter på ~9 femtosekunder (fs) integrert fra 100 Hz til 100 MHz. Design- og layoutteknikkene inne i ADF4401A muliggjør et typisk falsk-fritt dynamisk område på 90 dBc. En kapslingsstørrelse på 18 x 18 x 2,018 mm reduserer kortplassen vesentlig, sammenlignet med en tradisjonell frittstående (diskret) design.

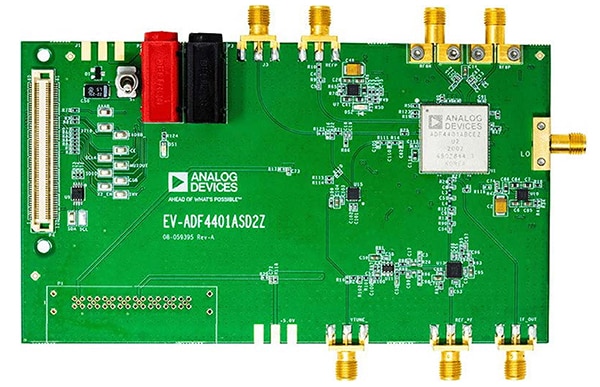

For å evaluere enhetens ytelse, kan designerne bruke evalueringskortet EV-ADF4401ASD2Z (figur 4). Kortet inkluderer en komplett translasjonsløkke, inkludert en ekstern PFD (HMC3716), et aktivt filter (LT6200) og en multiplekser (multiplexer) (ADG1609).

Figur 4: evalueringskort EV-ADF4401ASD2Z for translasjonsløkke-modul ADF4401A inkluderer en ekstern PFD, USB-tilkobling og spenningsregulatorer. (Bildekilde: Analog Devices)

Figur 4: evalueringskort EV-ADF4401ASD2Z for translasjonsløkke-modul ADF4401A inkluderer en ekstern PFD, USB-tilkobling og spenningsregulatorer. (Bildekilde: Analog Devices)

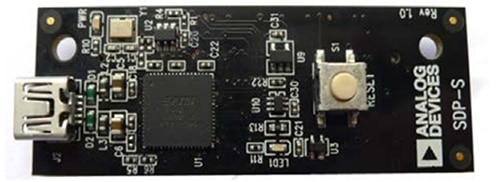

EV-ADF4401ASD2Z inkluderer ADF4401A TL SiP med integrert VCO, et sløyfefilter (5 MHz), en PFD, USB-tilkobling og spenningsregulatorer. I tillegg krever EV-ADF4401ASD2Z det (serielle) styringskortet EVAL-SDP-CS1Z for systemdemonstrasjon-plattform (system demonstrationsplattform – SDP) (figur 5). Kortet har USB-tilkobling fra en PC til EV-ADF4401ASD2Z, slik at det kan programmeres. Styringskortet er ikke inkludert i EV-ADF4401ASD2Z-settet.

Figur 5: EVAL-SDP-CS1Z (eller SDP-S)-styringskortet er nødvendig for å gi en USB-tilkobling fra EV-ADF4401ASD2Z til en PC, for programmering. (Bildekilde: Analog Devices)

Figur 5: EVAL-SDP-CS1Z (eller SDP-S)-styringskortet er nødvendig for å gi en USB-tilkobling fra EV-ADF4401ASD2Z til en PC, for programmering. (Bildekilde: Analog Devices)

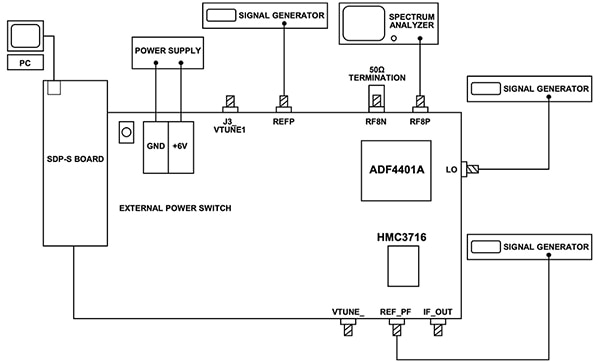

Figur 6 viser de fysiske tilkoblingene til EV-ADF4401ASD2Z-systemet. Den tilknyttede Analysis | Control | Evaluation (ACE)-programvaren styrer TL SiP-funksjonene. Strømforsyning kommer eksternt fra en 6-volts strømforsyning.

Figur 6: Et EV-ADF4401ASD2Z-oppsettskjema viser utstyret og tilkoblingene som kreves for å evaluere ADF4401A, inkludert SDP-S kontrollkortet, PC, strømforsyning, signalgeneratorer og spektrumanalysator. (Bildekilde: Analog Devices)

Figur 6: Et EV-ADF4401ASD2Z-oppsettskjema viser utstyret og tilkoblingene som kreves for å evaluere ADF4401A, inkludert SDP-S kontrollkortet, PC, strømforsyning, signalgeneratorer og spektrumanalysator. (Bildekilde: Analog Devices)

Det foreslåtte utstyret som skal brukes med dette evalueringskortet, inkluderer en Windows-PC, en spektrumanalysator eller en signalkildeanalysator og tre signalgeneratorer.

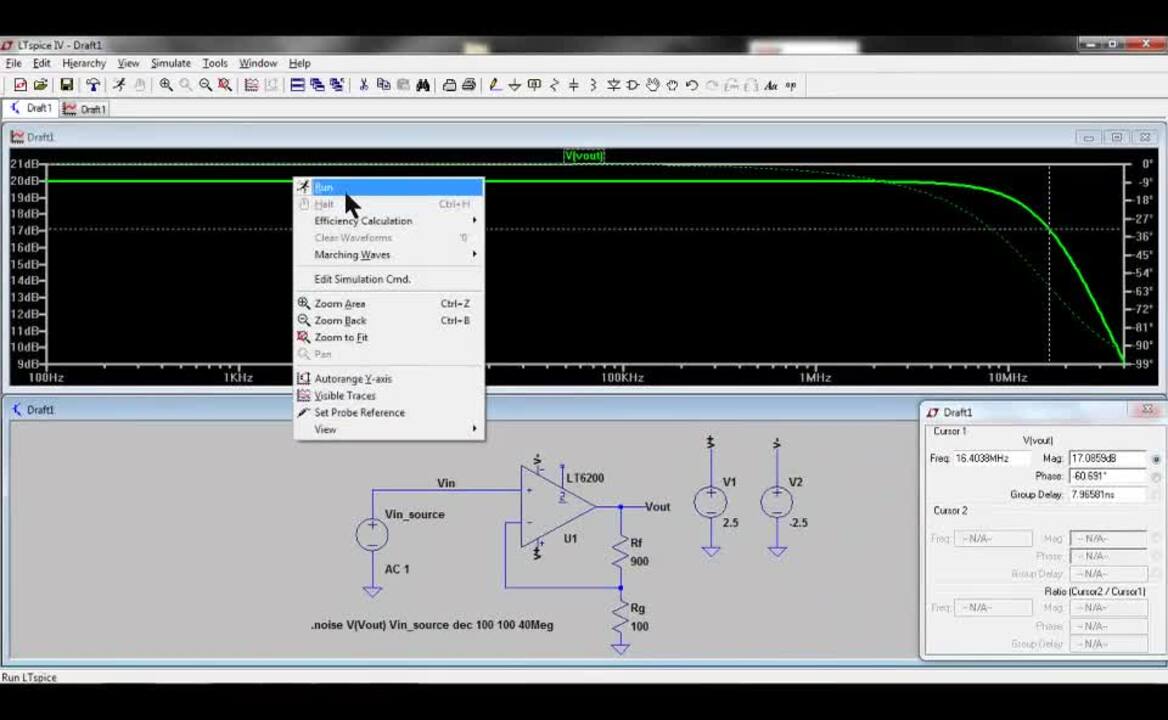

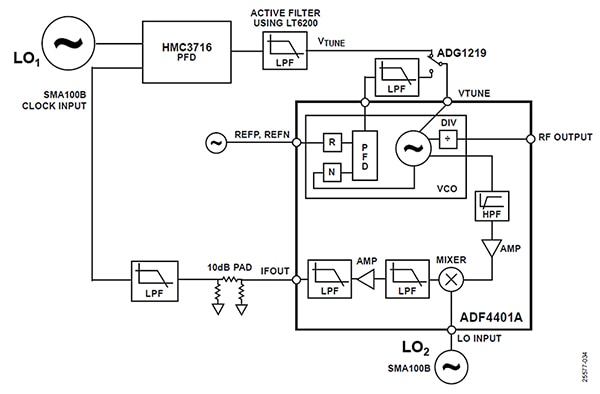

Blokkdiagrammet til EV-ADF4401ASD2Z viser ADF4401A-modulen, sammen med Analog Devices sin HMC3716 HMC3716-PFD, LT6200-op-amp og ADG1219-SPDT-bryteren (enpolet, toveis bryter) (figur 7).

Figur 7: EV-ADF4401ASD2Z-evalueringskortets blokkskjema viser nøkkelkomponentene som støtter AD4401A-translasjonsløkke. (Bildekilde: Analog Devices)

Figur 7: EV-ADF4401ASD2Z-evalueringskortets blokkskjema viser nøkkelkomponentene som støtter AD4401A-translasjonsløkke. (Bildekilde: Analog Devices)

Det er viktig å bruke en PFD som kan fungere på høye frekvenser, da dette minimerer behovet for delere, som kan forringe støyresponsen innenfor båndet. 1,3 GHz-fasesammenligningsfrekvensen til Analog Devices sin HMC3716 gjør den ideell for bruk i IF-området til ADF4401A. Evnen til en slik krets til å sammenligne både frekvens og fase eliminerer behovet for ytterligere kretser for å styre frekvensen til den tiltenkte utgangsfrekvensen. HMC3716 blir den eksterne PFD-en for å fullføre forskyvningssløyfen. Det høyfrekvente driftsområdet og ultra-lavfase støygulvet til HMC3716 gjør det mulig å designe sløyfefiltre med bred båndbredde.

I figur 7 demper operasjonsforsterker (op-amp) LT6200 med en LPF-konfigurasjon høyfrekvente sporer, mens veksler ADG1219 fullfører systemets translasjonsløkke.

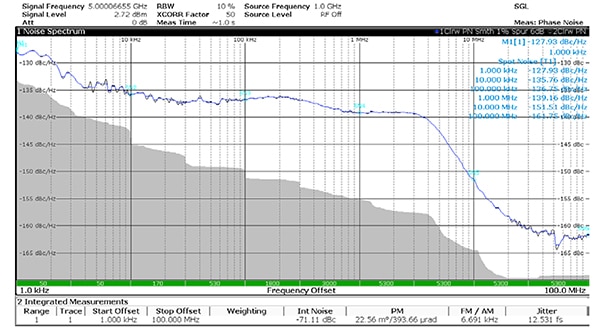

EV-ADF4401ASD2Z-evalueringsfiksturen oppretter støyplott innenfor båndet, samt jittermålinger, som vist i figur 8.

Figur 8: Enkeltstående sidebåndfasestøy ved 5 GHz-utgang, med en ekstern HMC3716-referanse på 500 MHz og ekstern LO ved 4,5 GHz. (Bildekilde: Analog Devices)

Figur 8: Enkeltstående sidebåndfasestøy ved 5 GHz-utgang, med en ekstern HMC3716-referanse på 500 MHz og ekstern LO ved 4,5 GHz. (Bildekilde: Analog Devices)

I figur 8 er LO2 og HMC3716-inngangen en SMA100B RF og mikrobølgesignalgenerator. Evalueringskortets LO2-støy innenfor båndet er ca. -135 dBc/Hz, som er tydelig ved lave forskyvninger (offsets), opp til 300 kHz. LO2, ADF4401A-modulen, HMC3716 PFD og sløyfefilteret bidrar til en innebygd støy på ca -140 dBc/Hz. Den interne fasestøyen vises mellom 5 MHz og 50 MHz, og fasestøygulvet i armaturet er ca. -160 dBc/Hz. Disse gir til sammen en rms jitter på 12,53 fs totalt.

Konklusjon

Høyhastighets-instrumenteringssystemer krever ekstremt lav-jitter klokker for å sikre at utdataene forblir kompromissløse. Utfordringen for ingeniører er å finne egnede enheter som kan bygge høyhastighets gigahertz-klokkesystemet. Translasjonsløkken ADF4401A forenkler i stor grad valg av enhet for å bygge klokkesystemet, og gir en kompakt modul som sikrer lav jitter ved høyere frekvenser, samtidig som den også reduserer brettplass, kostnader og tid til markedet.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.