Oppfyll mangfoldige funksjons- og sikkerhetskrav med flerkjerneprosessorer

Bidrag fra DigiKeys nordamerikanske redaktører

2020-10-01

Det forventes at styringer for bil, industri, robotikk, bygninger, samt styriger for andre kritiske integrerte systemutrustninger vil ta på seg flere forskjellige arbeidsbelastninger, som strekker seg fra sanntidsovervåking med lav effekt til multimediautrustninger på høyt nivå med grafisk display på flere displayer for grensesnitt mellom maskiner og mennesker (human-machine interfaces – HMI). Samtidig som de oppfyller disse brede funksjonskravene, må de også kunne støtte strenge sikkerhetsstandarder, lavere kostnader og fysisk størrelse, samt optimalisere balansen mellom effekt og ytelse.

For å oppfylle disse ofte motstridende kravene, har utviklere til dags dato blitt tvunget til enten å ofre funksjonsevne eller komplisere design og produksjon med ekstra enheter som trengs for å støtte spesifikke krav til blant annet grafikk og sikkerhet. Det utviklere virkelig trenger er en enkelt løsning som kan støtte et bredt spekter av produkter som oppfyller disse kravene på tvers av et bredt spekter av kritiske innebygde systemutrustninger.

Denne artikkelen beskriver raskt utviklingen av kritisk innebygd systemkonstruksjon. Den viser deretter hvordan flerkjernes bruksprosessorer – spesielt konstruert av NXP Semiconductors for å støtte en raskt utvidende liste over krav til både bred funksjonalitet og sikkerhetssertifiserbare egenskaper – kan brukes til å håndtere utvikleres utfordringer.

Utviklingen av hensyn til konstruksjon av integrerte systemer

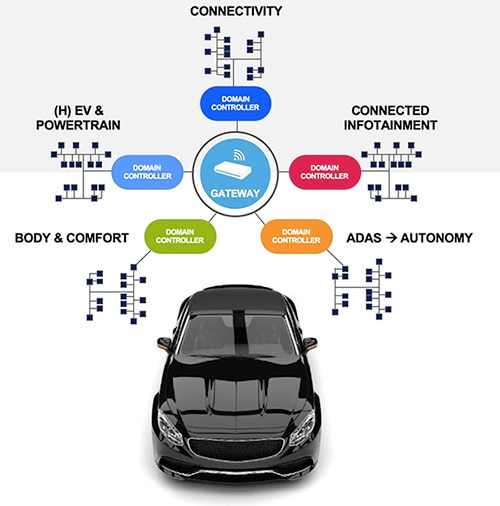

Den tradisjonelle rollen til innebygde enheter når det gjelder å støtte et begrenset sett med systemfunksjoner, er i stor grad erstattet av etterspørsel etter enheter som leverer bred kapasitet. I industrielle utrustninger krever for eksempel behovet for forbedrede HMI-funksjoner i smarte verktøy og utstyr at prosessorer kan levere optimalisert grafikk samtidig som de oppfyller mer tradisjonelle industrikrav i sanntid. På samme måte fører trenden i bilutrustninger mot hierarkiske arkitekturer som omfatter funksjonelle domenegrupper og gateway-er til et behov for prosessorer som fullt ut kan oppfylle disse kravene (figur 1).

Figur 1: Trenden som går mot mer hierarkiske bilsystemarkitekturer har skapt et behov for mer integrerte, skalerbare prosessorløsninger. (Bildekilde: NXP Semiconductors)

Figur 1: Trenden som går mot mer hierarkiske bilsystemarkitekturer har skapt et behov for mer integrerte, skalerbare prosessorløsninger. (Bildekilde: NXP Semiconductors)

Innenfor hvert funksjonelt domene fortsetter etterspørselen etter mer sofistikerte funksjoner å heve terskelen for ytelse og integrerte funksjoner. Fremveksten av displayer med bilde projisert på frontruten (heads-up display) krever for eksempel løsninger som kan sikre kontinuerlig levering av viktig grafisk informasjon til drivere. Sammen med disse neste generasjons displayene, legger det økende behovet for økt førervitenhet til ytterligere krav til kameragrensesnitt og høyytelsesutførelse av avansert gjenkjenningsprogramvare som kan gi søvnighetsdeteksjon.

Etter hvert som utrustninger fortsetter å utvikle seg, blir behovet for høyt integrerte, skalerbare løsninger viktigere for å møte stadig utvidede krav, samtidig som fysisk størrelse på konstruksjoner, kostnader og kompleksitet minimeres. Ved hjelp av NXP sin i.MX 8-familie av bruksprosessorer kan utviklere utnytte en kompatibel plattform av prosessorer med det spekteret av funksjoner og ytelse som trengs for å støtte et bredt spekter av brukskrav. Innenfor i.MX 8-familien adresserer NXP i.MX 8X-serien nye behov for sikkerhetssertifiserbare prosessorer som kreves i bil- og industriutrustninger i mellomklassen.

Flerkjernearkitektur håndterer ulike arbeidsbelastninger

En av vanskelighetene utviklere står overfor når de skal implementere enheter for bilindustrielle og industrielle applikasjoner, er den store bredden av krav. Der utviklere kan forvente å håndtere enten prosessering i sanntid eller ved prosessering av flere typer samtidige arbeidsbelastninger med høye nivåer, har etterspørselen etter intelligente delsystemer slått sammen disse vesentlig forskjellige typene databehandling. Utviklere trenger i økende grad løsninger som kan levere både pålitelig sanntidsrespons og høyytende brukerutførelse, samtidig som de støtter krav til funksjonssikkerhet.

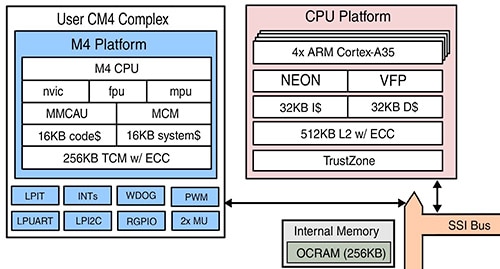

NXP i.MX 8X-serieprosessorer er utviklet for å levere sanntidsfunksjoner, høyytelsesprosessering og lavt strømforbruk, samt de utnytter fullt ut en sofistikert, flerkjernet CPU (central processing unit) for å håndtere ulike beregningsmessige arbeidsbelastninger (figur 2).

Figur 2: NXP i.MX 8X-serien bruker en flerkjernearkitektur som innbefatter en innebygd Arm Cortex-M4-prosessor (CM4) og flere Arm Cortex-A35-bruksprosessorer for å støtte blandede programvarearbeidsbelastninger. (Bildekilde: NXP Semiconductors)

Figur 2: NXP i.MX 8X-serien bruker en flerkjernearkitektur som innbefatter en innebygd Arm Cortex-M4-prosessor (CM4) og flere Arm Cortex-A35-bruksprosessorer for å støtte blandede programvarearbeidsbelastninger. (Bildekilde: NXP Semiconductors)

For sanntidsprosesseringsoppgaver av generelle formål inkluderer i.MX 8X-enheter: Arm Cortex-M4-prosessor (CM4) med flytepunktenhet (FPU), minnebeskyttelsesenhet (MPU), minnetilordnet kryptografisk akselerasjonsenhet (MMCAU) og tilleggskontrollmodul(MCM). For å støtte eksterne periferiutstyr som sensorer og aktuatorer kombinerer dette bruker-CM4-komplekset en nestet vektoravbruddskontroller (NVIC) med et omfattende sett med grensesnitt og moduler, inkludert periodisk avbruddstimer med lav effekt (LPIT), pulsbreddemodulasjon (PWM) og andre funksjoner som vanligvis kreves i bil- og industriutrustninger. Et par hurtigbufferminner og tett koblet minne (TCM) med mulighet for feilkorrigering av kode (ECC) bidrar til å minimere ekstern minnetilgang, hurtigeksekvering og håndtering av minnefeil.

For rask utførelse av utrustningenes arbeidsbelastninger omfatter CPU-plattformen flere Arm Cortex-A35-prosessorer (AP-er) med høy virkningsgrad – to AP-er i 8DualXPlus-prosessorer som MIMX8UX6AVLFZAC, samt fire AP-er i 8QuadXPlus-prosessorer som MIMX8QX6AVLFZAC. Sammen med dedikert instruksjons- (I$) og datahurtigbuffer (D$) inkluderer CPU-plattformen en delt 512 kilobyte (Kbyte) nivå 2-hurtigbuffer (L2) med ECC.

Arkitekturens Arm Cortex-A35-kjerner gir både programvarekompatibilitet og ytelsesskalerbarhet, samt støtter både 32-bits bakoverkompatibilitet og 64-biters ytelse. For ytterligere å fremskynde utførelsen av beregningsintensive algoritmer som signalbehandling og maskinlæring, gir Arm Cortex-A35-prosessorene vektorflytpunktbehandling (VFP) og Arm sin Neon single instruction multiple data (SIMD)-arkitekturutvidelser. For å akselerere utførelsen av programvare for bildebehandling, datamaskinvisjon og maskinlæring tilbyr Arm Compute Library funksjoner optimalisert for arkitekturer for Arm-prosessor og grafikkbehandlingsenhet (GPU), samt Ne10 C-biblioteket med åpen kildekode tilbyr Arm-optimaliserte funksjoner for beregningsintensive operasjoner.

Dedikerte motorer avlaster primære CPU-er

I tillegg til CM4-brukerkomplekset og Arm Cortex-A35 flerkjernet CPU-plattform, tilbyr arkitekturen ytterligere dedikerte motorer for multimediautrustninger. Sammen med en digital signalprosessor (DSP) for lyd- og talekodekbehandling, integrerer arkitekturen både en GPU og en videobehandlingsenhet (VPU). Enhetens GPU støtter standard grafikkbiblioteker, og akselererer operasjoner ved hjelp av fire separate firekomponenters flytende punktvektorer (vec4) med 16 utførelsesenheter og en 2-dimensjoners blit-motor med høy ytelse. VPU håndterer populære videoformater, akselererer dekoding opptil 4Kp30 (progressiv, 30 Hz) og koder opptil 1080p30. Brikkens dedikerte displaystyringblokk kan igjen levere grafikk (utgang) til så mange som tre uavhengige displayer.

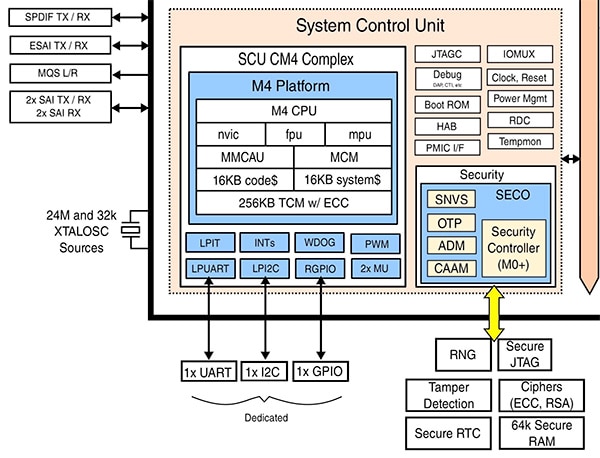

For ytterligere å maksimere ytelsen, integrerer i.MX 8X-arkitekturen også ytterligere prosessorkjerner designet for å frigjøre de primære CPU-plattformene fra den ekstra behandlingsbelastningen som vanligvis påløper ved utførelse av systemstyrings- og sikkerhetstjenester. Arkitekturens systemkontrollenhet (SCU) integrerer et CM4-kompleks som samsvarer med brukerens CM4-kompleks, men forblir dedikert fullstendig til SCU-operasjoner og utilgjengelig for bruk av utviklere (figur 3).

Figur 3: Dypt integrert inne i NXP i.MX 8X-prosessorer og utilgjengelig for utviklere, bruker SCU et dedikert Arm Cortex-M4-undersystem (CM4) for å laste av systemstyringsoppgaver fra enhetens hovedprosessorer. (Bildekilde: NXP Semiconductors)

Figur 3: Dypt integrert inne i NXP i.MX 8X-prosessorer og utilgjengelig for utviklere, bruker SCU et dedikert Arm Cortex-M4-undersystem (CM4) for å laste av systemstyringsoppgaver fra enhetens hovedprosessorer. (Bildekilde: NXP Semiconductors)

Sammen med å styring av strøm, klokkeslett og andre interne funksjoner, styrer SCU pinnemultipleksing og kanaldrivstyrkens inndata/utdata (I/O) under normal drift. Faktisk så kan CM4-brukerkomplekset og Arm Cortex-A35 AP-er ikke få direkte tilgang til disse ulike lavnivå maskinvarekapasitetene. I stedet tjener SCU til å distrahere disse funksjonene, så programvare som kjører på brukerens CM4 eller AP, ganske enkelt må kalle på SCU-ens firmware-API (application programming interface) som fungerer til å utføre funksjoner som å slå av unødvendige strømdomener. Hvis dette strømdomenet deles med en annen prosessor, bekrefter for eksempel SCU-en bare avslutningsforespørselen, men holder domenet påslått til den andre prosessoren også utsteder en avslutningsforespørsel.

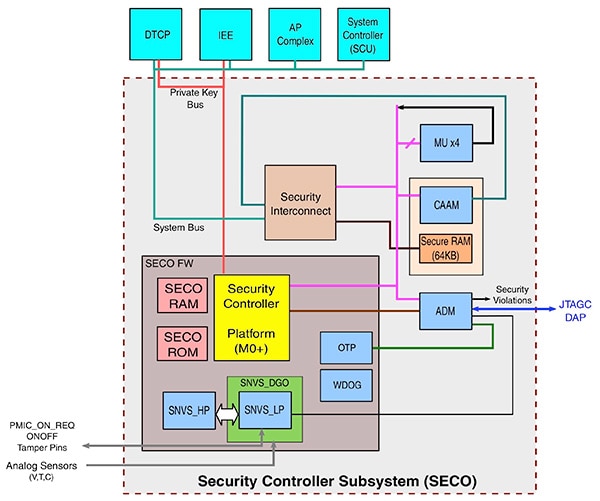

For å administrere i.MX 8X-enhetens omfattende sikkerhetsstøtte, kommer en annen dedikert prosessor inn i enhetens sikkerhetskontrollersystem (SECO). Innenfor SECO-undersystemet utfører en integrert laveffekt-arm-Cortex-M0+-prosessor firmware som støtter maskinvarebaserte sikkerhetsmuligheter, inkludert en privat busstilgang for sikre nøkler, engangsprogrammerbart minne (OTP) for sikker nøkkellagring og sikker ikke-flyktig lagring (SNVS) for ytterligere private data eller midlertidige nøkler (figur 4).

Figur 4: Innenfor NXP i.MX 8X sikkerhetskontrollersystemet (SECO) administrerer en dedikert laveffekt-arm Cortex-M0+-prosessor sikkerhetsoperasjoner, ved å trekke på en privat nøkkelbuss og flere maskinvaremoduler for sikker lagring, kryptografiakselerasjon og godkjent feilsøkingstilgang. (Bildekilde: NXP Semiconductors)

Figur 4: Innenfor NXP i.MX 8X sikkerhetskontrollersystemet (SECO) administrerer en dedikert laveffekt-arm Cortex-M0+-prosessor sikkerhetsoperasjoner, ved å trekke på en privat nøkkelbuss og flere maskinvaremoduler for sikker lagring, kryptografiakselerasjon og godkjent feilsøkingstilgang. (Bildekilde: NXP Semiconductors)

Utover disse kjernesikkerhetsmekanismene koordinerer SECO-undersystemet sikkerhetsoperasjoner for oppdagelse av manipulering og sikker feilsøking formidlet gjennom sin godkjente feilsøkingsmodul (ADM). For sikker utførelse støtter den integrerte CAAM-maskinvaresikkerhetsmodulen (Cryptographic Acceleration and Assurance Module) en full pakke med sikkerhetsalgoritmer, inkludert symmetrisk og asymmetrisk kryptografi, hashfunksjoner og en nummergenerator for tilfeldig nummer (RNG).

Under normal drift bruker enhetens behandlingsenheter, inkludert SCU, AP-er og DTCP-akselerator (Digital Transport Content Protection), SECO-sikkerhetsforbindelsen for å få tilgang til CAAM-funksjonalitet gjennom systembussen. Bortsett fra tilgang gjennom CAAM DMA-funksjonalitet (direct memory access), kan SECOS dedikerte Cortex-M0+-prosessor ikke få tilgang til systembussen. I stedet bruker den beskyttede interne tilkoblinger til å få tilgang til periferiutstyr, sikker tilgang til tilgjengelig RAM-minne (random access memory) og skrivebeskyttet ROM-minne (read-only memory – ROM), samt sin spesielle private nøkkelbuss.

Sammen med bruken av DTCP-akseleratoren spiller denne private nøkkelbussen en sentral rolle i i.MX 8X-prosessorstøtte for direktekryptering og dekryptering. Her bruker sikkerhetsprosessoren sine ressurser til å gi private nøkler som trengs av enhetens innebygde krypterings-/dekrypteringsmodul (IEE) når den leser sikkert fra eller skriver til kryptert lagring, uten involvering av den forespørende prosessoren, DMA-kontrolleren eller I/O-enheten.

SECO-undersystemet bygger på Arms TrustZone-teknologi integrert i enhetens Cortex-A35-prosessorer, samt det fungerer også med SCU under den sikre oppstartsprosessen. I denne prosessen tolker SCU oppstartsinnstillinger, konfigurerer oppstartskildene og laster oppstartsimage til internt eller eksternt minne. SECO-undersystemet bruker i sin tur sine kryptografifunksjoner til å godkjenne signerte firmwareimage etter at de er lastet inn, men før de utføres.

Sikring av kritiske displayer og kontrollfunksjonalitet

Selv om evnen til å behandle effektivt og sikkert ulike arbeidsbelastninger er viktig, er evnen til å beskytte viktige kapasiteter like viktig for oppgavekritiske utrustninger som de i bil- og industrisegmenter. NXP sin i.MX 8X-familie kombinerer sine prosessfunksjoner med sikkerhetssertifiserbare funksjoner som kreves for å oppfylle disse kritiske kravene.

Prosessorfamiliens sikkerhetsstøtte er innebygd på en rekke nivåer, med utgangspunkt i produksjon i en fullstendig utarmet prosessteknologi av silisium på isolator (FD-SOI) som forbedrer systemets pålitelighet. Fordi systemsikkerheten avhenger av et robust sikkerhetsgrunnlag, kan kombinasjonen av TrustZone-aktiverte AP-er, SECO-undersystemet og sikre oppstartsmuligheter gi den typen pålitelige omgivelser som trengs for å hindre trusler mot sikkerhet.

Samtidig bidrar evnen til uavhengig å håndtere tidskritiske oppgaver med CM4-brukerkomplekse og avlastningskritiske systemoppgaver til SCU- og SECO-undersystemene til å sikre at oppgavekritiske brukskapasiteter forblir tilgjengelige til tross for varierende behandlingsbelastning. Faktisk utvider NXP dette konseptet til å støtte oppdragskritiske displayer gjennom selskapets SafeAssure-teknologi, som integrerer en Automotive Safety Integrity Level B (ASIL B) -klar hardware-failover-bane i i.MX 8X-enheter. Med SafeAssure får brukerne automatisk en failover-avbildning hvis enheten oppdager en dataintegritet eller GPU-feil. Ved å kjøre i bakgrunnen, sikrer failover-avbildningen at kritisk informasjon forblir tilgjengelig selv under svikt i primærdisplayet.

Støtte for sikkerhetsinnretninger omfatter minnetilgang i i.MX 8X-baserte systemer. Blant de støttede minnegrensesnittene gir i.MX 8X-enheter 8-bits ECC for DDR3L-minne (Double Data Rate 3 low voltage). Sammen med ECC i L2-buffer (se figur 2 igjen) støtter denne DDR3L ECC-kapasiteten industrielt sikkerhetsintegritetsnivå 3 (SIL 3). I.MX 8X-arkitekturen utvider også ECC-støtte til eksterne flashlagringsenheter. Her gir en integrert Bose, Ray-Chaudhuri, Hocquenghem (BCH) -koder og dekodermodul 62-biters ECC som kan korrigere 2 til 20 enkelt-bits feil innenfor en blokk med data lest fra disse lagringsenhetene.

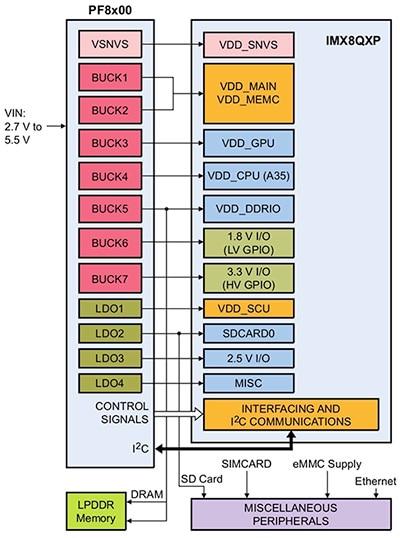

Bringer opp i.MX 8X-baserte applikasjoner

Som med alle prosessorer i denne klassen, krever implementering av en i.MX 8X-basert konstruksjon nøye oppmerksomhet på strenge krav til strøm, inkludert kritiske oppstartssekvenser. Oppstart av i.MX 8X-enheter krever å hente strøm i sekvens eller samtidig til fire forskjellige forsyningsgrupper, som starter med SVN-undersystemet og fortsetter med SCU-en, I/O-ene og minnegrensesnittene, og til slutt resten av enheten. Utviklere kan oppfylle dette kravet bare ved hjelp av NXP sin PF8x00 strømstyringsintegrerte kretsenheter (PMIC), som gir et komplett sett med spenningsnivåer (spenningsskinner) og styresignaler som trengs for å støtte i.MX 8X-prosessorer samt eksternt minne og typiske systemperiferiutstyr (figur 5).

Figur 5: NXP PF8x00 PMIC-er gir et komplett sett med spenningsnivåer (spenningsskinner) og styresignaler som trengs for å drive i.MX 8X-prosessorer. (Bildekilde: NXP Semiconductors)

Figur 5: NXP PF8x00 PMIC-er gir et komplett sett med spenningsnivåer (spenningsskinner) og styresignaler som trengs for å drive i.MX 8X-prosessorer. (Bildekilde: NXP Semiconductors)

Når utviklere implementerer sine egne i.MX 8X-baserte design, kan de bruke NXP MC33PF8100CCES PMIC som er forhåndsprogrammert for bruk med 8QuadXPlus-prosessorer som MIMX8QX6AVLFZAC. Andre PF8x00-varianter som MC33PF8100A0ES og MC33PF8200A0ES støtter i.MX 8X-prosessorer, men er ikke forhåndsprogrammert.

For sikkerhetsinnretninger integrerer PF8200-serieenheter som MC33PF8200A0ES funksjoner som er utviklet for å støtte ASIL B-systemer. Sammen med flere interne skjermer, inkludert en utgangsspenningsskjerm med en dedikert referanse for båndavstand (enegritap), inkluderer PF8200 PMIC-er en feilsikker utgangspinne (FSOB) utformet for å holde systemet i en sikker tilstand under oppstart eller under en strømbruddshendelse. I tillegg tester en analog innebygd selvtest (ABIST) rutine alle spenningsskjermer mens en selvtest rutine verifiserer annen enhetsfunksjonalitet.

Selv om PF8x00 PMIC-er kan forenkle maskinvareutformingen av i.MX 8X-baserte systemer, må noen utviklere kanskje umiddelbart begynne å evaluere i.MX 8X-enheter og raskt prototype i.MX 8X-baserte applikasjoner. NXP sin MCIMX8QXP-CPU-i.MX 8X Multisensory Enablement Kit (MEK) gir en klar utviklingsplattform som kombinerer et NXP i.MX 8QuadXPlus-prosessor, NXP F8100 PMIC, 3 gigabyte (Gbyte) RAM, 32 Gbyte innebygd Multi-Media Controller-minne (eMMC) og 64 megabyte (Mbyte) flashminne. Sammen med display-, kamera- og lydgrensesnitt inkluderer MEK-kortet et sett sensorer som vanligvis brukes i bilindustri eller i industriell bruk. For ytterligere tilkoblings-, lyd- og utvidelsesalternativer kan utviklere også legge til NXP sitt valgfrie MCIMX8-8X-BB-basiskort som leveres som tilleggsutstyr.

Konklusjon

For et økende antall applikasjoner som bil-, industri-, bygningskontroll- og HMI-applikasjoner, har prosesseringsarbeidsbelastningen utvidet seg til å omfatte både tradisjonell sanntids I/O-prosessering og ny applikasjonsnivåprosessering med multimediagrafikk. Selv om det finnes designalternativer for hver type arbeidsbelastning, er det få tilgjengelige løsninger som oppfyller det økende behovet for energieffektive løsninger med høy ytelse som kan tilfredsstille krav til sikkerhetssertifiserbare konstruksjoner i bilindustrielle og industrielle anvendelser.

Som vist, ved bruk av en familie av flerkjerneprosessorer fra NXP Semiconductors, kan utviklere mer effektivt implementere design som kan oppfylle disse ulike kravene og skalere enkelt for å håndtere nye krav til høy ytelse.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.