Slik bruker du FPGA SoC-er for sikre og tilkoblede harde sanntidssystemer

Bidrag fra DigiKeys nordamerikanske redaktører

2023-02-16

Feltprogrammerbare portmatriser (FPGA – field programmable gate array), Linux-kompatible RISC-V MCU-delsystemer (MCU – microcontroller unit – mikrokontroller), avanserte minnearkitekturer og høyytelses kommunikasjonsgrensesnitt, er viktige verktøy for konstruktører. Dette gjelder spesielt for konstruktører av sikre tilkoblede systemer, sikkerhetskritiske systemer og et bredt spekter av deterministiske sanntidssystemer, slik som kunstig intelligens (AI) og maskinlæring (ML).

Integreringen av disse forskjellige elementene i et sikkert, tilkoblet og deterministisk system kan imidlertid være en utfordrende og tidkrevende aktivitet, akkurat som å legge ut høyhastighetsforbindelsene for de forskjellige systemelementene. Konstruktører må inkludere en minnestyringsenhet, minnebeskyttelsesenhet, sikker oppstartsfunksjonalitet og transceivere i gigabit-klassen for høyhastighetskonnektivitet. Konstruksjonen vil kreve aktiv og statisk strømstyring og regulering av innkoblingsstrømstøt. Noen konstruksjoner vil kreve drift over det utvidede kommersielle temperaturområdet for grenseskikttemperaturen, fra 0 °C til +100 °C (TJ), mens systemer i industrielle miljøer må fungere med TJ fra –40 °C til +100 °C.

For å løse disse og andre utfordringer kan konstruktører bruke FPGA-enheter med system på brikke (SoC – system-on-chip) som kombinerer lavt strømforbruk, termisk effektivitet og sikkerhet i forsvarsklassen, for smarte, tilkoblede og deterministiske systemer.

Denne artikkelen gjennomgår arkitekturen til en slik FPGA SoC og ser på hvordan den støtter den effektive konstruksjonen av tilkoblede og deterministiske systemer. Den gir deretter en kort presentasjon av referanseverdien for EEMBC CoreMark-Pro prosessorkraft kontra strømforbruk, sammen med en visning av benchmarken til en representativ FPGA SoC. Det ser på hvordan sikkerheten er innbakt i disse FPGA SoC-ene og gir detaljerte eksempler på typiske FPGA SoC-er fra Microchip Technology, samt en utviklingsplattform for å akselerere konstruksjonsprosessen. Den avslutter med en kort liste over utvidelseskort fra MikroElektronika, som kan brukes til å implementere en rekke kommunikasjonsgrensesnitt, samt posisjonsmuligheter for det globale navigasjonssatellittsystemet, GNSS.

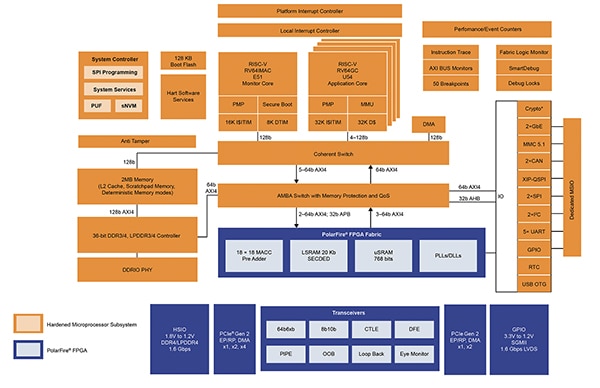

SoC-er konstruert med FPGA-struktur

Brikken for denne SoC-en er en FPGA-struktur som inneholder systemelementene, fra FPGA-en til RISC-V MCU-delsystemet som er konstruert med hard FPGA-logikk. MCU-delsystemet omfatter en firekjernet (quad core) RISC-V MCU-klynge, en RISC-V-monitorkjerne, en systemstyring og et minnedelsystem for deterministisk nivå 2 (L2). FPGA-en i disse SoC-ene inkluderer opptil 460 K logiske elementer, transceivere på opptil 12,7 gigabit per sekund (Gb/s) og andre inngangs-/utgangsblokker (I/O-blokker), inkludert generell I/O (GPIO – general purpose I/O) og PCIe 2 (PCIe – Peripheral Component Interconnect Express). Den overordnede arkitekturen er konstruert for pålitelighet. Den inkluderer korrigering for enkeltfeil og deteksjon av dobbeltfeil (SECDED – single-error correction and double-error detection) på alle minner, differensialeffektanalyse (DPA – differential power analysis), fysisk minnebeskyttelse og 128 kilobit (kb) flash-oppstartsminne (figur 1).

Figur 1: Alle elementene i denne FPGA SoC-en, inkludert RISC-V-delsystemene, er implementert på FPGA-strukturen. (Bildekilde: Microchip Technology)

Figur 1: Alle elementene i denne FPGA SoC-en, inkludert RISC-V-delsystemene, er implementert på FPGA-strukturen. (Bildekilde: Microchip Technology)

Microchip tilbyr sitt Mi-V-økosystem (Mi-V uttales «my five» på engelsk) av tredjepartsverktøy og konstruksjonsressurser for å støtte implementeringen av RISC-V-systemer. Den er bygget for å fremskynde bruken av RISC-V-instruksjonssettarkitekturen (ISA – instruction set architecture) for harde RISC-V-kjerner og for myke RISC-V-kjerner. Elementer i Mi-V-økosystemet omfatter tilgang til:

- Lisenser for immaterielle rettigheter (IP)

- Maskinvare

- Operativsystemer og mellomvare

- Feilsøkere, kompilatorer og designtjenester

De harde RISC-V MCU-ene i FPGA SoC-en inkluderer flere feilsøkingsfunksjoner, for eksempel passiv kjøretidskonfigurerbar AXI (AXI – advanced extensible interface) og instruksjonssporing. AXI gjør det mulig for konstruktører å overvåke data som skrives til eller leses fra ulike minner, i tillegg til å vite når det skrives eller leses.

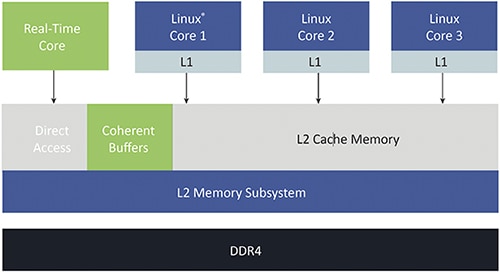

RISC-V MCU-delsystemet bruker en ett-trinns, sekvensiell, fem-trinns pipeline. Den er ikke sårbar for Spectre- eller Meltdown-utnyttelser, som kan ramme arkitekturer i defekt tilstand. Alle fem MCU-ene er forbundet (koherent) med minnedelsystemet, og støtter en blanding av deterministiske sanntidssystemer i AMP-modus (AMP – asymmetric multi-processing) og Linux. Funksjonene til RISC-V-delsystemet omfatter følgende (figur 2):

- Kjør Linux og harde sanntidsoperasjoner

- Konfigurer L1 og L2 som deterministisk minne

- Delsystem for DDR4-minne

- Deaktiver/aktiver forgreningsprediktorer

- Sekvensiell pipeline-drift

Figur 2: RISC-V-delsystemet omfatter flere prosessor- og minneelementer. (Bildekilde: Microchip Technology)

Figur 2: RISC-V-delsystemet omfatter flere prosessor- og minneelementer. (Bildekilde: Microchip Technology)

Mer prosessering med mindre energi

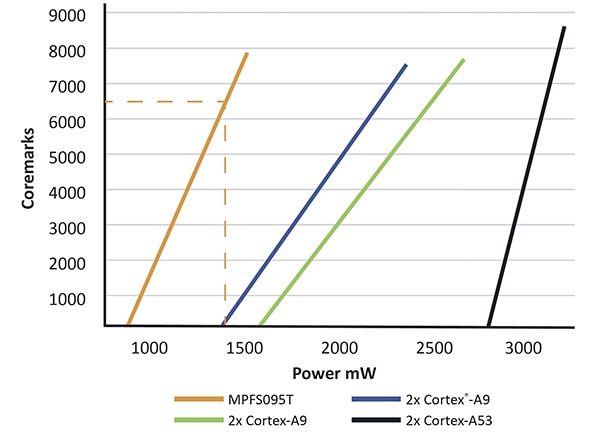

I tillegg til fordelene forbundet med systemdrift, inkludert støtten for hard prosessering i sanntid, er disse FPGA SoC-ene svært energieffektive. EEMBC CoreMark-PRO-benchmark er en bransjestandard for å sammenligne virkningsgraden og ytelsen til mikrokontrollere (MCU-er) i innebygde systemer. Den ble konstruert spesielt for å teste maskinvarens benchmark-ytelse og erstatte Dhrystone-benchmarken.

CoreMark-PRO-arbeidsbelastningene inkluderer et mangfold av ytelsesegenskaper, parallellitet på instruksjonsnivå og minneutnyttelse basert på fire flytetalls-arbeidsbelastninger og fem vanlige heltallsarbeidsbelastninger. Flytetalls-arbeidsbelastningene inkluderer en lineær algebrarutine avledet fra LINPACK, en hurtig fouriertransform (FFT), en algoritme med nevralnett for mønsterevaluering, samt en forbedret versjon av Livermore-sløyfebenchmarken. JPEG-komprimering, en XML-analysealgoritme (XML-parser), ZIP-komprimering og en 256-bits SHA-256-algoritme (SHA – secure hash algorithm) danner grunnlaget for heltallsarbeidsbelastningene.

MPFSO95T-modellene av disse SoC FPGA-ene, for eksempel MPFS095TL-FCSG536E, kan levere opptil 6500 CoreMark ved 1,3 watt (figur 3).

Figur 3: MPFS095T FPGA SoC (oransje linje) leverer 6500 CoreMark ved 1,3 watt. (Bildekilde: Microchip Technology)

Figur 3: MPFS095T FPGA SoC (oransje linje) leverer 6500 CoreMark ved 1,3 watt. (Bildekilde: Microchip Technology)

Sikkerhetsfaktorer

De sikkerhetskritiske og harde sanntidsbruksområdene til disse FPGA SoC-ene krever kraftig sikkerhet, i tillegg til høy energieffektivitet og kraftige prosesseringsegenskaper. De grunnleggende sikkerhetsfunksjonene til disse FPGA SoC-ene inkluderer differensialeffektanalyse (DPA – differential power analysis), bestandig bitstrømprogrammering, en sann tilfeldig tall-generator (TRNG – true random number generator) og en fysisk ikke-klonbar funksjon (PUF – physical unclonable function). De inkluderer også standard og brukerdefinert sikker oppstart (secure boot), fysisk minnebeskyttelse som gir minnetilgangsbegrensninger knyttet til maskinens privilegiumstilstand, inkludert maskin, overvåker eller brukermoduser, og immunitet mot Meltdown- og Spectre-angrep.

Sikkerhet begynner med sikker styring av forsyningskjeden, inkludert bruken av maskinvarebaserte sikkerhetsmoduler (HSM – hardware security module) under wafertesting og -innkapsling. Bruken av et 768-byte digitalt signert x.509 FPGA-sertifikat som er innebygd i hver FPGA SoC, bidrar til å sikre forsyningskjeden.

Mange integrerte sabotasjedetektorer er inkludert i disse FPGA SoC-ene for å gi sikker og pålitelig drift. Hvis sabotasje detekteres, utstedes et sabotasjeflagg som gjør det mulig for systemet å respondere etter behov. Noen av de tilgjengelige sabotasjedetektorene omfatter følgende:

- Spenningsmonitorer

- Temperatursensorer

- Klokkefeil- og klokkefrekvensdetektorer

- JTAG aktiv detektor

- Maske (mesh) aktiv detektor

Sikkerhet er ytterligere sikret med AES-256-mottiltak mot korrelert strømangrep (CPA – correlation power attack) via symmetrisk blokkchiffer, integrerte kryptografiske oversiktsmuligheter for å sikre dataintegritet, integrert PUF for nøkkellagring, samt nullstillbare evner for FPGA-struktur og alle integrerte minner.

Eksempler på FPGA SoC

Microchip Technology kombinerer disse funksjonene og teknologiene i sine PolarFire FPGA SoC-er, med flere hastighetsklasser, temperaturklassifiseringer og forskjellige kapslingsstørrelser, for å støtte behovene til konstruktører for et bredt spekter av løsninger med mellom 25.000 og 460.000 logiske elementer. Fire temperaturklasser er tilgjengelige (alle klassifisert for TJ): 0 °C til +100 °C er utvidet kommersielt område; –40 °C til +100 °C er industrielt område; –40 °C til +125 °C er bilindustriens område; og –55 °C til +125 °C er militært område.

Konstruktører kan velge mellom enheter med standard hastighetsklasse eller enheter med hastighetsklasse –1 som er 15 % raskere. Disse FPGA SoC-ene kan fungere ved 1,0 volt for drift med lavest effekt eller ved 1,05 volt for høyere ytelse. De er tilgjengelige i en rekke kapslingsstørrelser, deriblant 11 x 11 millimeter (mm), 16 x 16 mm og 19 x 19 mm.

For konstruksjoner som trenger utvidet kommersiell temperaturdrift, standard hastighetsdrift og 254.000 logiske elementer i en kapsling på 19 x 19 mm, kan konstruktører bruke MPFS250T-FCVG484EES. For enklere løsninger som trenger 23.000 logiske elementer, kan konstruktører bruke MPFS025T-FCVG484E. Denne kommer også med utvidet kommersiell temperaturdrift og standard hastighetsklasse i en kapsling på 19 x 19 mm. MPFS250T-1FCSG536T2 med 254.000 logiske elementer er konstruert for høyytelses systemer for bilindustrien og har et driftstemperaturområde på –40 til 125 °C og en –1-hastighetsklasse som gir 15 % raskere klokke, i en kompakt kapsling på 16 x 16 mm med 536 kuler som har en senteravstand på 0,5 mm (figur 4).

Figur 4: MPFS250T-1FCSG536T2 for kjøretøytemperatur kommer i en kapsling på 16 x 16 mm med 536 kuler som har en senteravstand på 0,5 mm. (Bildekilde: Microchip Technology)

Figur 4: MPFS250T-1FCSG536T2 for kjøretøytemperatur kommer i en kapsling på 16 x 16 mm med 536 kuler som har en senteravstand på 0,5 mm. (Bildekilde: Microchip Technology)

FPGA SoC-utviklingsplattform

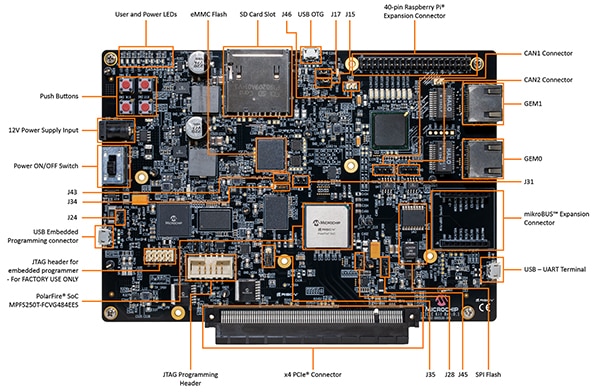

For å fremskynde konstruksjonen av systemer med PolarFire FPGA SoC-en, tilbyr Microchip MPFS-ICICLE-KIT-ES PolarFire SoC Icicle-settet. Dette settet muliggjør utforskning av det laveffekts Linux-kapable RISC-V-mikroprosessorsystemet med fem kjerner og sanntidseksekvering. Settet inneholder en gratis Libero Silver-lisens som er nødvendig for å evaluere konstruksjoner. Den støtter programmerings- og feilsøkingsfunksjoner på ett språk.

Disse FPGA SoC-ene støttes med programvareutviklingssettet (SDK – software development kit) for VectorBlox-akseleratoren som muliggjør AI/ML-konstruksjoner med lav effekt og liten formfaktor. Hovedvekten ligger på å forenkle konstruksjonsprosessen til et slik nivå at konstruktører ikke trenger å ha noen FPGA-konstruksjonserfaring. SDK-en for VectorBlox-akseleratoren gjør det mulig for utviklere å programmere energieffektive nevrale nettverk ved å bruke C/C++. Icicle-settet har mange funksjoner for å tilby et omfattende utviklingsmiljø, for eksempel et strømsensorsystem for flere skinner som kan overvåke de ulike strømdomenene, PCIe-rotporten og innebygde minner – inkludert LPDDR4, QSPI og eMMC Flash – for å kjøre Linux og Raspberry Pi, og mikroBUS-utvidelsesporter for en rekke kablede og trådløse tilkoblingsalternativer, pluss funksjonelle utvidelser som GNSS-posisjonsfunksjonalitet (figur 5).

Figur 5: Dette omfattende FPGA SoC-utviklingsmiljøet inkluderer kontakter for Raspberry Pi- (øverst til høyre) og microBUS-utvidelseskort (nederst til høyre). (Bildekilde: Microchip Technology)

Figur 5: Dette omfattende FPGA SoC-utviklingsmiljøet inkluderer kontakter for Raspberry Pi- (øverst til høyre) og microBUS-utvidelseskort (nederst til høyre). (Bildekilde: Microchip Technology)

Utvidelseskort (ekspansjonskort)

Noen eksempler på mikroBUS-utvidelseskort omfatter:

MIKROE-986, for å legge til CAN-busskonnektivitet ved å bruke et serielt periferigrensesnitt (SPI – serial peripheral interface).

MIKROE-1582, for tilkobling mellom mikrokontrolleren og en RS-232-buss.

MIKROE-989, for tilkobling med en RS422/485-kommunikasjonsbuss.

MIKROE-3144 støtter LTE Cat M1- og NB1-teknologiene som muliggjør pålitelig og enkel tilkobling med 3GPP IoT-enheter.

MIKROE-2670 muliggjør GNSS-funksjonalitet med samtidig mottak av GPS- og Galileo-konstellasjoner, i tillegg til enten BeiDou eller GLONASS, noe som resulterer i høy posisjonsnøyaktighet i situasjoner med svake signaler eller forstyrrelser i urbane kløfter.

Konklusjon

Konstruktører kan bruke FPGA SoC-er når de utvikler tilkoblede, sikkerhetskritiske og harde deterministiske sanntidssystemer. FPGA SoC-er gir et bredt spekter av systemelementer, deriblant en FPGA-struktur, et RISC-V MCU-delsystem med høyytelsesminner, kommunikasjonsgrensesnitt med høy hastighet og mange sikkerhetsfunksjoner. For å hjelpe konstruktører med å komme i gang, er utviklingskort og miljøer tilgjengelige som inkluderer alle nødvendige elementer, for eksempel utvidelseskort som kan brukes til å implementere et bredt spekter av kommunikasjons- og posisjonsfunksjoner.

Anbefalt lesing

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.