Grunnleggende om frekvensgeneratorer med fasereguleringssløyfe

Bidrag fra DigiKeys nordamerikanske redaktører

2021-02-03

Stigende datahastigheter i høyhastighetsbusser med seriellkommunikasjon krever systemklokker som har høyere frekvenser, overlegen stabilitet, større frekvensoppløsning og høyere signalklarhet. Direkte digitale frekvensgeneratorer (synthesizer) tilbyr disse egenskapene, men kun for frekvenser under 2 eller 3 gigahertz (GHz). En løsning er nødvendig for frekvenser på opptil flere titalls gigahertz.

Denne løsningen begynner med analoge frekvensgeneratorer basert på fasereguleringssløyfer (PLL – phase locked loop) som genererer klokkefrekvenser på opptil 30 GHz. Deretter benytter heltall-N-frekvensgeneratorer (som multipliserer referansefrekvensen med et heltall) og fraksjonell-N-frekvensgeneratorer (som multipliserer referansefrekvensen med fraksjonelle (ikke-heltall) verdier) spesielle teknikker som minimerer fasestøy og lignende urenheter i signalet.

Denne artikkelen beskriver konstruksjonen av både heltall-N- og fraksjonell-N-frekvensgeneratorer ved å bruke eksempelenheter fra Analog Devices. Artikkelen fremhever også innovasjonene som gjør det mulig for disse enhetene å brukes i serielle dataforbindelser med høye hastigheter, samt for radarer som bruker frekvenssprangmetode.

Heltall-N-frekvensgeneratorer med fasereguleringssløyfe

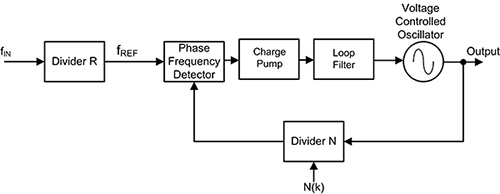

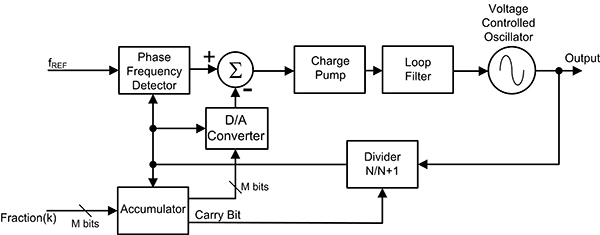

PLL-kretser brukes for frekvens- og fasestyring. De kan konfigureres som klokkekilder, frekvensmultiplikatorer, demodulatorer, sporingsgeneratorer eller klokkegjenopprettingskretser. Hver av disse bruksområdene krever forskjellige egenskaper, men alle bruker det samme grunnleggende kretskonseptet. Figur 1 viser et blokkskjema over en grunnleggende PLL som er konfigurert som en frekvensmultiplikator.

Figur 1: Blokkskjema over en klassisk heltall-N-frekvensgenerator med fasereguleringssløyfe. (Bildekilde: DigiKey)

Figur 1: Blokkskjema over en klassisk heltall-N-frekvensgenerator med fasereguleringssløyfe. (Bildekilde: DigiKey)

Betjeningen av denne kretsen er typisk for alle fasereguleringssløyfer. Det er kort fortalt et reguleringssystem som styrer fasen til en spenningsstyrt oscillator (VCO – voltage-controlled oscillator). Inngangssignalet påføres en frekvensdeler (pre-scaling divider), som deler inngangsfrekvensen med en faktor R. Utgangen til frekvensdeleren er referansefrekvensen, som danner én inngang på en fasefrekvensdetektor (PFD – phase-frequency detector).

Den andre PFD-inngangen er et reguleringssignal fra utgangen til en del-med-N-teller (divide-by-N-counter). Normalt, hvis PLL-en er låst, vil frekvensene til begge signalene være nesten like. Utgangen til fasedetektoren er en spenning som er proporsjonal med faseforskjellen mellom de to inngangene. Hvis sløyfen er ulåst, noe som skjer ved oppstart eller hvis det er en stor øyeblikkelig endring i inngangsfrekvensen, vil fasefrekvensdetektoren styre PLL-driftsfrekvensen til ønsket innstilling. Når denne frekvensen er oppnådd, returnerer PFD-en til fasedetektormodus og har en utgangsverdi som er proporsjonal med faseforskjellen mellom referansefrekvensen og reguleringssignalet.

Fasefrekvensdetektoren driver en matepumpe, som er en topolet bryterkoblet strømkilde. Dette betyr at den kan sende positive og negative strømpulser inn i sløyfefilteret til PLL-en.

Sløyfefilteret jevner ut fasefeilsignalet og fastsetter også de dynamiske egenskapene til PLL-en. Det filtrerte signalet styrer VCO-en. Vær oppmerksom på at utgangen til VCO-en har en frekvens som er N ganger inngangsverdien som forsynes til frekvensreferanseinngangen til fasefrekvensdetektoren, og er N/R ganger frekvensinngangen. Dette utgangssignalet sendes tilbake til fasedetektoren via del-med-N-telleren (divide by N counter).

Vanligvis er sløyfefilteret konstruert for å samsvare med egenskapene som er påkrevet av konstruksjonen til PLL-en. Hvis PLL-en skal anskaffe og spore et signal, vil båndbredden til sløyfefiltret være større enn om det forventet en fast inngangsfrekvens. Frekvensområdet som PLL-en vil akseptere og låse seg til, kalles «fangstområdet» (capture range). Når PLL-en er låst og sporer et signal, kalles frekvensområdet som PLL-en vil følge, «sporingsområdet» (tracking range). Sporingsområdet er vanligvis større enn fangstområdet. PLL-sløyfefilteret fastsetter også hvor raskt signalfrekvensen kan endres og fortsatt opprettholde låsen, dvs. den maksimale stigehastigheten. Jo smalere båndbredden til sløyfefilteret er, desto mindre er den oppnåelige fasefeilen. Dette er på bekostning av tregere respons og redusert fangstområde. PLL-er som brukes i klokkeinstallasjoner opererer hovedsakelig på faste frekvenser. Båndbredden til sløyfefilteret skal som hovedregel være mye mindre enn referansefrekvensen.

Fordi PLL-utgangsfrekvensen er et heltall-multiplum av referansefrekvensen, er frekvensoppløsningen lik referansefrekvensen. For å oppnå en mer detaljert frekvensoppløsning må du redusere referansefrekvensen, noe som gjøres med frekvensdeler-telleren R.

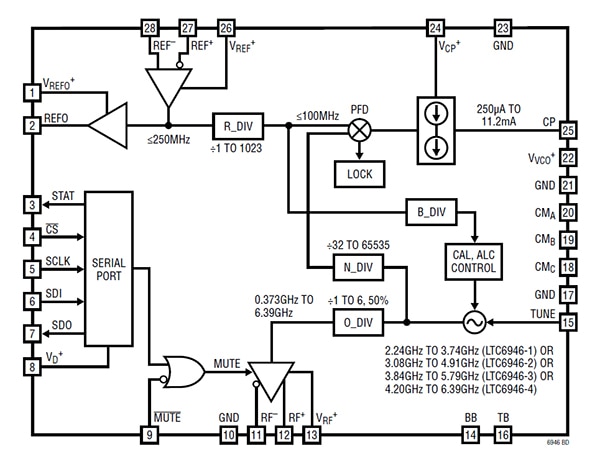

Et kommersielt eksempel på en heltall-N-frekvensgenerator er Analog Devices sin LTC6946IUFD-3#PBF, en lavstøys frekvensdeler på 0,64 til 5,79 GHz med en integrert VCO og utmerket kunstig (spurious) ytelse (figur 2). Den er medlem av en familie på fire frekvensgenerator-IC-er, der hver av disse har forskjellig frekvensområde, og dekker et totalt område fra 0,373 til 6,390 GHz.

Figur 2: Blokkskjemaet til Analog Devices sine LTC6946IUFD-3#PBF heltall-N-frekvensgeneratorer med integrert VCO. (Bildekilde: Analog Devices)

Figur 2: Blokkskjemaet til Analog Devices sine LTC6946IUFD-3#PBF heltall-N-frekvensgeneratorer med integrert VCO. (Bildekilde: Analog Devices)

Denne frekvensgeneratoren krever et eksternt brukerforsynt sløyfefilter, som kan optimaliseres for den bestemte installasjonen. Det er en intern frekvensdeler-teller med et deleområde fra 1 til 1023. Sløyfefrekvensdeleren har et område fra 32 til 65535. Matepumpestrømmen kan justeres fra 250 mikroampere (μA) til 11,2 milliampere (mA) for å samsvare med kravene til sløyfefilteret.

Fraksjonell-N-frekvensgeneratorer med fasereguleringssløyfe

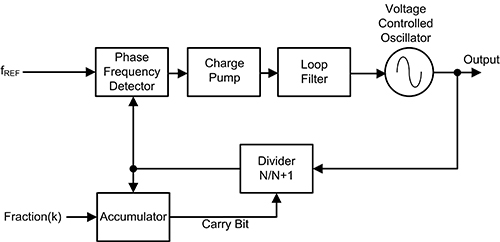

Frekvensoppløsningen til PLL-frekvensgeneratoren kan forbedres ved å redusere trinnstørrelsen til mindre enn heltallverdier, dvs. lage fraksjonelle trinn i sløyfefrekvensdeleren (N). Dette oppnås ved hjelp av dynamisk variasjon eller «dithering» av nedtellingsverdien. Dette betyr at frekvensdelerinnstillingen holder verdien N i et fast antall sykluser av PLL-utgangsfrekvensen, og blir med jevne mellomrom trinnvis justert til en annen verdi, for eksempel N+1. For eksempel, hvis frekvensdelerinnstillingen er 4 i tre referanseperioder og 5 for den fjerde referansesyklusen, vil den effektive nedtellingen være 4,25. En måte å oppnå dette på er å bruke en akkumulator, slik det er vist i figur 3.

Figur 3: Blokkskjemaet til en fraksjonell-N PLL-frekvensgenerator som bruker en akkumulator til å modulere frekvensdelertellingen. (Bildekilde: DigiKey)

Figur 3: Blokkskjemaet til en fraksjonell-N PLL-frekvensgenerator som bruker en akkumulator til å modulere frekvensdelertellingen. (Bildekilde: DigiKey)

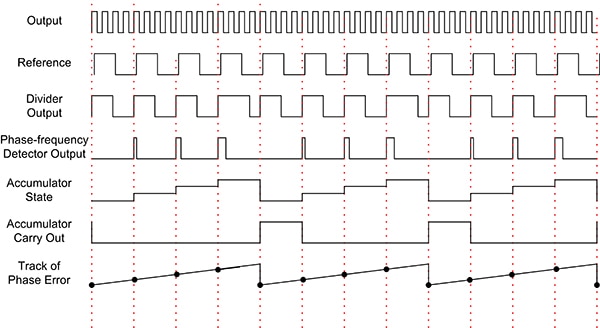

Akkumulatoren teller utgangspulsene fra frekvensdeleren, og hver M, der M er akkumulatorens modul, sender ut en overføringsbit som endrer frekvensdelerinngangen. Figur 4 fortsetter eksemplet med å angi en fraksjonell frekvensdelerinnstilling på 4,25.

Figur 4: Timingskjema for en fraksjonell-N-frekvensgenerator som bruker en akkumulator. (Bildekilde: DigiKey)

Figur 4: Timingskjema for en fraksjonell-N-frekvensgenerator som bruker en akkumulator. (Bildekilde: DigiKey)

Akkumulatoren drives av den delte utgangen og teller modulo fire, dvs. M er lik fire. Den genererer en bæreutgang hver fjerde puls, som øker frekvensdelertelleren med én. Akkumulatoren nullstilles og begynner å telle igjen. Økningen i frekvensdelerinnstillingen skifter utgangsfrekvensen, noe som resulterer i en akkumulert faseforskyvningsfeil. Sporet for fasefeil viser pulsverdien som en funksjon av tiden.

Den gjennomsnittlige frekvensdelerinnstillingen er 4,25, men frekvensgeneratorutgangen er fasemodulert, noe som resulterer i kunstige toner i utgangen. Hvis man ser på akkumulatortilstanden, er det åpenbart at den sporer fasefeilen. Dette kan brukes til å fjerne modulasjonen, slik det er vist i figur 5.

Figur 5: Bruke D/A-konvertert akkumulatortilstand til å avbryte fasemoduleringen på grunn av fraksjonell-N-ditheringen. (Bildekilde: DigiKey)

Figur 5: Bruke D/A-konvertert akkumulatortilstand til å avbryte fasemoduleringen på grunn av fraksjonell-N-ditheringen. (Bildekilde: DigiKey)

Akkumulatortilstanden konverteres til analog av en digital-til-analog (D/A)-omformer og skaleres og subtraheres fra fasefrekvensdetektorutgangen for å avbryte fasemoduleringen på grunn av fraksjonell-N-ditheringen. Dette må gjøres med stor forsiktighet. Hvis korreksjonssignalet ikke samsvarer nøyaktig med fasefeilen, vil dette resultere i kunstige toner på utgangen.

Oppgi sigma-delta-modulatoren

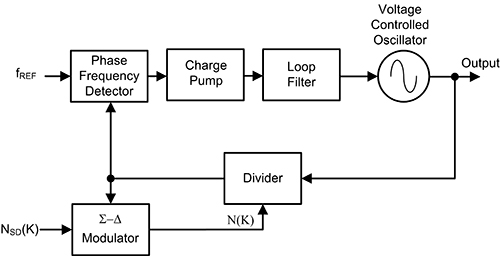

Periodisiteten i akkumulatoren er årsaken til kunstige utganger fra frekvensgeneratoren. Hvis akkumulatoren erstattes av en sigma-delta-modulator, kan digitale teknikker brukes til å modulere frekvensdelertelleren på en måte som minimerer kunstige responser og støy. Denne erstatningen vises i figur 6.

Figur 6: Når akkumulatoren byttes ut med en sigma-delta-modulator, er det mulig å bruke digitale teknikker til å variere frekvensdelertellingen for å redusere kunstige responser. (Bildekilde: DigiKey)

Figur 6: Når akkumulatoren byttes ut med en sigma-delta-modulator, er det mulig å bruke digitale teknikker til å variere frekvensdelertellingen for å redusere kunstige responser. (Bildekilde: DigiKey)

Det er to vanlige digitale teknikker som brukes i sigma-delta-moduleringstopologien. Den første innebærer å øke antallet N-frekvensdelertellinger over et større område av verdier på en slik måte at den gjennomsnittlige delingsfaktoren vil produsere den ønskede fraksjonelle frekvensdelerverdien. Dette vil redusere de primære fraksjonelle forstyrrelsene (spurs). Den akkumulatorbaserte frekvensgeneratoren varierer tellingen mellom to tilstander. Dette er en førsteordens moduleringsmetode. En n-ordens sigma-delta fraksjonell PLL modulerer N-telleren mellom 2n forskjellige verdier. For eksempel vil en tredjeordens modulator veksle mellom åtte forskjellige frekvensdelerverdier, og en fjerdeordens modulator vil veksle mellom 16 forskjellige frekvensdelerverdier.

Den andre digitale teknikken – også referert til som dithering – innebærer å randomisere 2N-sekvensen slik at den er pseudotilfeldig. Samtidig som den opprettholder et gjennomsnittlig fraksjonelt frekvensdelerforhold, konverterer den de fraksjonelle forstyrrelsene til formet tilfeldig støy på en slik måte at det kan filtreres av PLL-en.

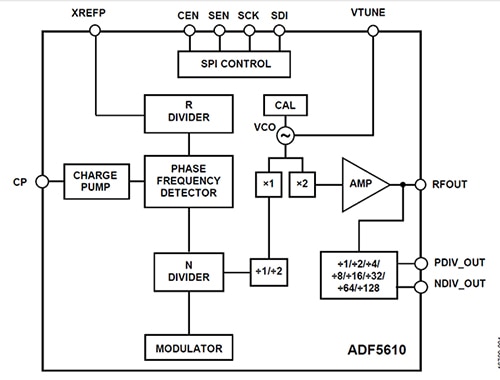

En kommersiell versjon av en sigma-delta fraksjonell-N-frekvensgenerator er Analog Devices sin ADF5610BCCZ, som er en lavstøys 0,57 MHz til 14,6 GHz fraksjonell-N-frekvensgenerator med integrert VCO (figur 7).

Figur 7: Et blokkskjema over Analog Devices ADF5610BCCZ, som støtter både fraksjonell-N-konfigurasjoner eller heltall-frekvensgeneratorkonfigurasjoner. (Bildekilde: Analog Devices)

Figur 7: Et blokkskjema over Analog Devices ADF5610BCCZ, som støtter både fraksjonell-N-konfigurasjoner eller heltall-frekvensgeneratorkonfigurasjoner. (Bildekilde: Analog Devices)

ADF5610 krever en ekstern referanseoscillator og et sløyfefilter. Den har en integrert VCO med en grunnleggende frekvens fra 3650 MHz til 7300 MHz. Disse frekvensene dobles internt og sendes til RFOUT-pinnen. Det er en differensialutgang som gjør det mulig for den doblede VCO-frekvensen å deles med faktorene 1, 2, 4, 8, 16, 32, 64 eller 128, noe som gjør det mulig å generere RF-utgangsfrekvenser helt ned til 57 MHz.

ADF5610 bruker en avansert sigma-delta-modulator med en 24-biters fraksjonell modul som oppnår eksepsjonelt lave kunstige nivåer. I likhet med alle frekvensgeneratorer som bruker en sigma-delta-modulator, bruker denne enheten digital signalbehandlingsteknikk til å finne ønsket gjennomsnittlig fraksjonelt frekvensdelerforhold. Denne prosessen, som er klokket til PFD-hastigheten, produserer utgangsmodulasjonsstøy kalt kvantiseringsstøy med høypass-frekvensrespons. Det eksterne lavpass-sløyfefilteret brukes til å filtrere denne kvantiseringsstøyen til et nivå under fasestøyen til VCO-en, og forhindrer dermed støyen fra å bidra til systemets samlede fasestøy.

ADF5610 inkluderer også en nøyaktig frekvensmodus for frekvensfeil på 0 hertz (Hz). Denne modusen er i stand til å generere eksakte frekvenser mellom tilstøtende heltall-N-grensetrinn, samtidig som de bruker den fulle 24-biters faseakkumulatormodulen. Den oppnår nøyaktige frekvenstrinn med en høyfaset detektorsammenligningshastighet, noe som gjør at PLL-en kan opprettholde utmerket ytelse når det kommer til fasestøy og kunstige signaler i denne modusen.

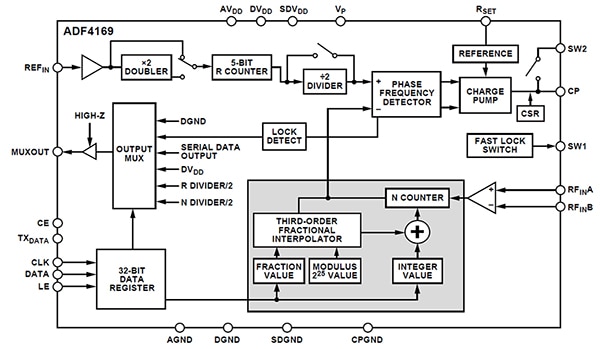

Analog Devices ADF4169CCPZ-RL7 er en annen PLL-frekvensgenerator som kan konfigureres som enten en heltall-N- eller fraksjonell-N-enhet. Den opererer med en RF-båndbredde på opptil 13,5 GHz med modulering og bølgeformgenerering. Den bruker en ekstern referansefrekvensinngang, en VCO og et sløyfefilter. Den har en tredjeordens sigma-delta-modulator for fraksjonell-N-syntese som kan deaktiveres, noe som gjør at enheten kan kjøre i heltall-N-modus (figur 8).

Figur 8: Analog Devices ADF4169CCPZ-RL7 bruker en tredjeordens sigma-delta-modulator. (Bildekilde: Analog Devices)

Figur 8: Analog Devices ADF4169CCPZ-RL7 bruker en tredjeordens sigma-delta-modulator. (Bildekilde: Analog Devices)

ADF4158WCCPZ-RL7-frekvensgeneratoren er tiltenkt for bruk i radarer med frekvensmodulert kontinuerlig bølge (FMCW – frequency modulated continuous wave). Den kan håndtere forskjellige typer modulerte bølgeformer i frekvensdomenet, inkludert sagtann- og trekant-ramper. Dette er en spesiell funksjon som er nødvendig i radarinstallasjoner.

Konklusjon

Stigende datahastigheter i høyhastighets seriellkommunikasjonsbusser krever at teknikere vurderer andre direkte digitale frekvensgeneratorer – som fungerer best under 3 GHz – for systemklokkeløsninger. PLL-baserte frekvensgeneratorer som bruker heltall-N- og fraksjonell-N-topologier, gir stabile signaler med lav støy for bruksområder med høyfrekvente klokker, seriell datakommunikasjon og radar, for frekvenser på opptil flere titalls gigahertz.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.