Co-prosessorarkitekturen: En innebygd systemarkitektur for rask prototyping

2021-07-06

Redaktørens merknad – selv om den er godt kjent for den digitale prosesseringsytelsen sin, samt gjennomstrømning, gir co-prosessorarkitekturen de innebygde systemene designermulighetene til å implementere prosjektledelsesstrategier, som forbedrer både utviklingskostnader og tid før ferdig produkt kommer ut på markedet. Denne artikkelen, som fokuserer spesielt på kombinasjonen av en diskret mikrokontroller (MCU) og en frittstående (diskret) feltprogrammerbar portmatrise (FPGA), viser hvordan denne arkitekturen egner seg for en effektiv og gjentagende (iterativ) designprosess. Fordelene ved denne arkitekturen utforskes ved å utnytte forskningskilder, erfaringsmessige (empiriske) funn og case-studier, samt eksemplariske utrustninger oppgis. Ved denne artikkelens konklusjon vil den innebygde systemdesigneren ha en bedre forståelse av når og hvordan denne allsidige maskinvarearkitekturen skal implementeres.

Introduksjon

Designeren av det innebygde systemet får før eller senere utfordringer med designbegrensninger, ytelsesforventninger og tids- og budsjettproblemer. Faktisk, så understreker selv motsetningene i moderne prosjektledelse moteord og setninger ytterligere den prekære karakteren av denne rollen: «mislykkes fort«; «være smidig»; «fremtidssikre det»; og «være forstyrrende!». Akrobatikken som er involvert i selv å prøve å tilfredsstille disse forventningene kan være rystende, og likevel har de blitt snakket og fortsetter å bli forsterket over hele markedet. Det som trengs, er en designtilnærming, som gjør at en evolusjonær gjentagende (iterativ) prosess kan implementeres, akkurat som med de fleste innebygde systemer, starter den med maskinvarearkitekturen.

Co-prosessorarkitekturen, en maskinvarearkitektur som er kjent for å kombinere styrkene til både mikrokontrollerenhet (MCU) og feltprogrammerbar gate-array (FPGA)-teknologi, kan tilby integrasjonsdesigneren av den innebygde en prosess som kan oppfylle selv de mest krevende kravene, og likevel gir den den fleksibiliteten som er nødvendig for å håndtere både kjente og ukjente utfordringer. Ved å tilby maskinvare som kan tilpasses gjentagende (iterativt), kan designeren demonstrere fremgang, treffe kritiske milepæler og dra full nytte av den raske prototypeprosessen.

Innenfor denne prosessen er sentrale prosjektmilepæler, hver med sin egen unike verdi å tilføre utviklingsarbeidet. Gjennom hele denne artikkelen vil disse bli referert til med følgende termer: Milepælen for den digitale signalbehandlingen med mikrokontrolleren, milepælen for systemadministrasjonen med mikrokontrolleren og milepælen for produktutvikling (produktdesign).

I slutten av av denne artikkelen vil det bli vist at en fleksibel maskinvarearkitektur kan være bedre egnet for moderne integrert systemdesign enn en mer stiv tilnærming. Videre kan denne tilnærmingen føre til forbedringer av både prosjektkostnad og tid før ferdig produkt kommer ut på markedet. Argumenter, eksempler og case-studier vil bli brukt til å forsvare denne posisjonen. Ved å observere verdien av hver milepæl innenfor designfleksibiliteten denne arkitekturen har, blir det klart at en adaptiv maskinvarearkitektur er en kraftig drivkraft når det gjelder å presse konstruksjonen av innebygde systemer fremover.

Utforske styrkene til co-prosessorarkitekturen: designfleksibilitet og prosessering med høy ytelse

Et vanlig bruksområde for FPGA-design er å grensesnitt direkte med en høyhastighets ADC-omformer (analog-til-digital-omformer). Signalet digitaliseres, leses inn i FPGA-en, og deretter brukes noen digitale signalprosessoralgoritmer (DSP) på dette signalet. Sist av alt tar FPGA-en deretter beslutninger basert på funnene.

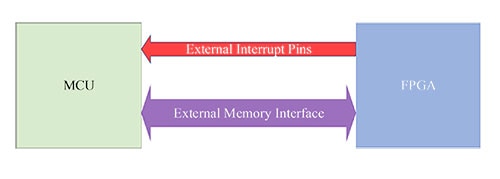

En slik utrustning vil tjene som eksempel gjennom hele denne artikkelen. Videre illustrerer figur 1 en generisk co-prosessorarkitektur, der MCU og FPGA er koblet sammen gjennom MCU-ens eksterne minnegrensesnitt. FPGA-en blir behandlet som om det var et stykke eksternt statisk tilfeldig tilgangsminne (static random-access memory – SRAM). Signaler kommer tilbake til Mikrokontrolleren (MCU-en) fra FPGA-en og fungerer som maskinvareavbruddslinjer og statusindikatorer. Dette gjør det mulig for FPGA-en å indikere kritiske tilstander til mikroprosessoren (MCU-en), for eksempel å kommunisere at en ADC-konvertering er klar, eller at en feil har oppstått, eller at en annen bemerkelsesverdig hendelse har skjedd.

Figur 1: Generisk co-prosessordiagram (MCU + FPGA). (Bildekilde: CEPD)

Figur 1: Generisk co-prosessordiagram (MCU + FPGA). (Bildekilde: CEPD)

Styrkene ved co-prosessor-tilnærmingen vises sannsynligvis best innenfor resultatene av hver av de ovennevnte milepælene. Verdien vurderes ikke bare ved å liste opp prestasjonene i en oppgave eller fase, men også ved å vurdere aktiveringen som disse prestasjonene tillater. Svarene på følgende spørsmål bidrar til å vurdere den samlede verdien av en milepæls leveranser:

- Kan fremgangen til andre teammedlemmer nå fortsette raskere etter hvert som prosjektavhengigheter og flaskehalser fjernes?

- Hvordan muliggjør prestasjonene til milepælen ytterligere parallelle utførelsesbaner?

Den digitale signalbehandlingen med milepælen for mikrokontroller

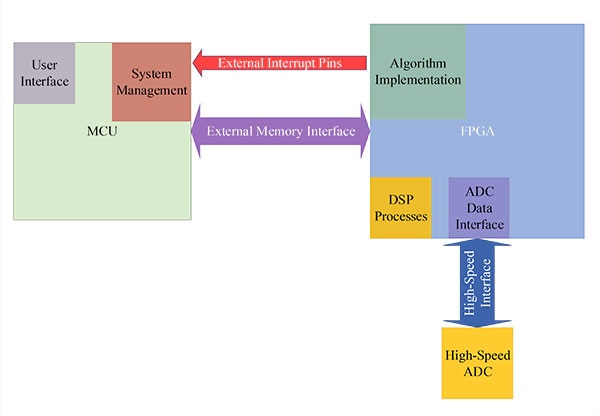

Figur 2: Arkitektur - digital signalbehandling med mikrokontrolleren. (Bildekilde: CEPD)

Figur 2: Arkitektur - digital signalbehandling med mikrokontrolleren. (Bildekilde: CEPD)

Det første utviklingsstadiet som denne maskinvarearkitekturen tillater plassering av MCU-en foran og i midten. Alt i alt er mikrokontrolleren (MCU-en) og kjørbar programvareutvikling mindre ressurskrevende og tidkrevende enn FPGA- og maskinvarebeskrivende språkutvikling (HDL). Ved å starte produktutvikling med MCU-en som den primære prosessoren, kan algoritmer implementeres, testes og valideres raskere. Dette gjør det mulig å oppdage algoritmiske og logiske feil tidlig i konstruksjonsprosessen, og dette gjør det også mulig å teste og validere betydelige deler av signalkjeden.

FPGAs rolle i denne første milepælen er å fungere som et høyhastighets grensesnitt for datainnsamling. Dens oppgave er å på en pålitelig måte overføre data fra høyhastighets-ADC-en, varsle MCU-en om at data er tilgjengelige og presentere disse dataene på MCUs eksterne minnegrensesnitt. Selv om denne rollen ikke inkluderer implementering av HDL-baserte DSP-prosesser eller andre algoritmer, er den likevel svært kritisk.

FPGA-utviklingen utført i denne fasen legger grunnlaget for produktets ultimate suksess både innenfor produktutviklingsarbeidet og når det slippes på markedet. Ved å fokusere på bare grensesnittet på lavt nivå, kan tilstrekkelig tid brukes til å teste disse viktige operasjonene. Først når FPGA pålitelig og trygt utfører denne grensesnittrollen, kan denne milepælen avsluttes trygt.

Viktige resultater fra denne første milepælen inkluderer følgende fordeler:

- Hele signalstien - alle forsterkninger, dempninger og konverteringer - vil ha blitt testet og validert.

- Prosjektets utviklingstid og krefter vil ha blitt redusert ved først å implementere algoritmene i programvare (C / C ++); Dette er av betydelig verdi for ledelsen og andre interessenter, som må se gjennomførbarheten av dette prosjektet før de godkjenner fremtidige designfaser.

- Leksjonene fra implementering av algoritmene i C / C ++ vil kunne overføres direkte til HDL-implementeringer - ved bruk av programvare-til-HDL-verktøy, for eksempel Xilinx HLS.

Systemadministrasjonen med mikrokontroller milepæl

Figur 3: Arkitektur - systemadministrasjon med mikrokontrolleren. (Bildekilde: CEPD)

Figur 3: Arkitektur - systemadministrasjon med mikrokontrolleren. (Bildekilde: CEPD)

Det andre utviklingsstadiet, som denne co-prosessortilnærmingen tilbyr, defineres ved å flytte DSP-prosesser og algoritmeimplementeringer fra MCU-en til FPGA-en. FPGA er fortsatt ansvarlig for høyhastighets ADC-grensesnitt, men ved å anta disse andre rollene blir hastigheten og parallelliteten som tilbys av FPGA utnyttet fullt ut. I tillegg til, i motsetning til MCU, kan flere forekomster av DSP-prosesser og algoritmekanaler implementeres, og kjøres samtidig.

Bygget på leksjonen fra MCUs implementering, bærer designeren denne tilliten videre til denne neste milepælen. Verktøy, som det nevnteVivado HLS fra Xilinx, gi en funksjonell oversettelse fra den kjørbare C / C ++ - koden til syntetiserbar HDL. Nå må tidsbegrensninger, prosessparametere og andre brukerpreferanser fortsatt defineres og implementeres, men kjernefunksjonaliteten vedholdes og oversettes til FPGA-stoffet.

For denne milepælen er MCUs rolle som systemansvarlig. Status- og kontrollregister i FPGA overvåkes, oppdateres og rapporteres av MCU. Videre administrerer MCU-en brukergrensesnittet (UI). Dette brukergrensesnittet kan ha form av webserveren som er tilgjengelig via et Ethernet- eller Wi-Fi-tilkobling, eller det kan være et industrielt berøringsskjermgrensesnitt som gir tilgang til brukere på bruksstedet. Den viktigste løsningen fra MCU-ens nye, mer raffinerte rolle er dette: Ved å bli fritatt fra de beregningsintensive prosesseringsoppgavene, blir nå både MCU og FPGA utnyttet i oppgaver som de er godt egnet for.

Nøkkelresultater utgjør denne milepælen og inkluderer disse fordelene:

- Rask, parallell gjennomføring av DSP-prosesser og algoritmeimplementeringer blir gitt av FPGA.MCU-en gir et responsivt og strømlinjeformet brukergrensesnitt og styrer produktets prosesser.

- Etter å ha blitt utviklet og validert i MCU, har algoritmiske risikoer blitt dempet, og disse begrensningene blir oversatt til syntetiserbar HDL. Verktøy, for eksempelVivado HLS , gjør denne oversettelsen til en enklere prosess. Videre kan FPGA-spesifikke risikoer reduseres gjennom integrerte simuleringsverktøy, som Vivado-designpakken.

- Interessenter er ikke utsatt for betydelig risiko ved å flytte prosessene til FPGA. Tvert imot får de se og nyte fordelene som FPGAs hastighet og parallellitet gir. Målbare ytelsesforbedringer blir observert, og det kan nå fokuseres på å klargjøre denne designen for produksjon.

Milepælen for produktutvikling (produktdesign)

Med den databehandlingskrevende prosessen som tas opp i FPGA-en, og MCU-en som håndterer sine systemadministrasjons- og brukergrensesnittroller, er produktet klart for distribusjon. Denne artikkelen taler ikke for å omgå Alpha og Beta-utgivelser, men vektleggingen for denne milepælen er funksjonene som co-prosessorarkitekturen gir for produktutvikling (produktdesign).

Både MCU-en og FPGA-en er feltoppdaterbare enheter. Flere fremskritt er gjort for å gjøre FPGA-oppdateringer like tilgjengelige som programvareoppdateringer. Dessuten, siden FPGA-en Oppdateringer kan planlegges, distribueres og tilpasses per sluttbruker. Sist av alt kan bruker- og brukstilfelle-logger vedlikeholdes og knyttes til spesifikke byggeimplementasjoner. Fra disse datasettene kan ytelsen fortsette å bli raffinert og forbedret selv etter at produktet er i felt.

Kanskje styrkene ved denne totale systemmatemuligheten ikke er mer understreket enn i rombaserte utrustninger. Når et produkt er lansert, må vedlikehold og oppdateringer utføres eksternt. Dette kan være så enkelt som å endre logiske forhold, eller så komplisert som å oppdatere et kommunikasjonsmoduleringsskjema. Programmerbarheten som tilbys av FPGA-teknologier og co-prosessorarkitekturen kan imøtekomme hele dette spekteret av funksjoner, samtidig som de tilbyr strålingsherdede komponentvalg.

Den siste viktige løsningen fra denne milepælen er progressiv kostnadsreduksjon. Kostnadsreduksjoner, endringer i materiallister (BOM) og andre optimaliseringer kan også forekomme i denne milepælen. Under feltutplasseringer kan det oppdages at produktet kan fungere like bra med en billigere MCU, eller mindre i stand FPGA. På grunn av co-prosessoren sitter ikke arkitekturdesignere fast ved hjelp av komponenter hvis kapasitet overstiger utrustningens behov. Videre, hvis en komponent blir utilgjengelig, tillater arkitekturen at nye komponenter integreres i designet. Dette er ikke tilfellet med en enkelt brikke, system på en brikke (SoC)-arkitektur, eller med en høyytelses DSP eller MCU som forsøker å håndtere hele produktets prosessering. Co-prosessorarkitekturen er en god blanding av kapasitet og fleksibilitet som gir designeren flere valg og friheter både med utviklingsfasene og ved lansering på markedet.

Støtte til forskning og relaterte case-studier

Eksempel på satellittkommunikasjon

Kort sagt er verdien av en co-prosessor å avlaste den primære prosessorenheten slik at oppgaver utføres på maskinvare, der akselerasjoner og effektivisering kan utnyttes. Fordelen med et slikt designvalg er en netto økning i beregningshastighet og evner, og som denne artikkelen hevder, en reduksjon i utviklingskostnader og utviklingstid. Kanskje en av de mest overbevisende områdene for disse fordelene, er innen romkommunikasjonssystemer.

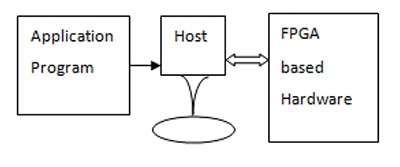

G. Prasad og N. Vasantha beskriver i publikasjonen FPGA-basert maskinvare som koprosessor hvordan databehandling innenfor en FPGA blander beregningsbehovene til satellittkommunikasjonssystemer uten de høye engangskostnadene for spesifikke integrerte kretser (ASIC) for utrustningen eller de spesifikke begrensningene for utrustningen til en hardarkitekturprosessor. Akkurat som det ble beskrevet i Digital Signal Processing med Microcontroller-milepælen, begynner designet med at utrustningens prosessor utfører et flertall av de beregningsintensive algoritmene. Fra dette utgangspunktet identifiserer de nøkkelseksjonene i programvaren som bruker et flertall av klokkesyklusene til sentral prosesseringsenhet (CPU) og overfører disse seksjonene til HDL-implementering. Den grafiske fremstillingen er veldig lik den som har blitt presentert så langt, men de har valgt å representereutrustningens program som sin egen uavhengige blokk, slik den enten kan realiseres iVerten (vertsprosessoren) eller iFPGA-basert maskinvare .

Figur 4: Utrustningens program, vertsprosessor og FPGA-basert maskinvare - brukt i eksempel på satellittkommunikasjon.

Figur 4: Utrustningens program, vertsprosessor og FPGA-basert maskinvare - brukt i eksempel på satellittkommunikasjon.

Ved å bruke et perifert komponent interconnect (PCI) -grensesnitt og vertsprosessorens direkte minnetilgang (DMA), økes perifer ytelse dramatisk. Dette observeres stort sett innenfor forbedringene forDerandomiserings-prosess. Da denne prosessen ble utført i programvaren til vertsprosessoren, var det tydelig en flaskehals i systemets sanntidsrespons. Imidlertid ble følgende fordeler observert når de ble flyttet til FPGA:

- DeDerandomisering prosess utført i sanntid uten å forårsake flaskehalser

- Vertsprosessorens beregningsomkostninger ble betydelig redusert, og den kunne nå bedre utføre en ønsket loggerolle.

- Den totale ytelsen til hele systemet ble oppskalert.

Alt dette ble oppnådd uten kostnadene forbundet med en ASIC, og mens du nyter fleksibiliteten til programmerbar logikk [5]. Satellittkommunikasjon byr på betydelige utfordringer, og denne tilnærmingen kan verifiserbart oppfylle disse kravene og fortsette å gi designfleksibilitet.

Eksempel på bilinfo

Underholdningssystemer i biler er kjennetegn ved kresne forbrukere. I motsetning til et flertall av bilelektronikk, er disse enhetene svært synlige og forventes å gi eksepsjonell responstid og ytelse. Imidlertid blir designere ofte presset mellom de nåværende behovene til designet og fleksibiliteten, som fremtidige funksjoner vil kreve. For dette eksempel vil implementeringsbehovene for signalbehandling og trådløs kommunikasjon bli brukt til å fremheve styrkene til maskinvarearkitekturen for co-prosessorer.

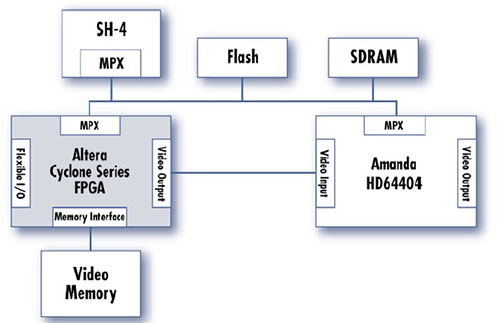

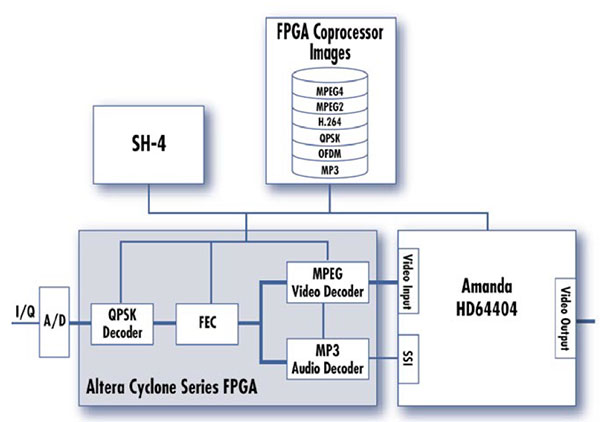

En av de dominerende arkitektonene for bilunderholdningssystemer som ble brukt, ble utgitt av Delphi Delco Electronics Systems Corporation. Denne arkitekturen brukte en SH-4 MCU med en ledsager ASIC, Hitachi'sHD64404 Amanda perifer. Denne arkitekturen tilfredsstilte over 75 % av bilmarkedets grunnleggende underholdningsfunksjonalitet; det manglet imidlertid muligheten til å adressere utrustninger for videobehandling og trådløs kommunikasjon. Ved å inkludere en FPGA i denne eksisterende arkitekturen, kan ytterligere fleksibilitet og kapasitet legges til denne allerede eksisterende designtilnærmingen.

Bilde av infotainment FPGA-co-prosessorarkitektur eksempel 1.

Bilde av infotainment FPGA-co-prosessorarkitektur eksempel 1.

Figur 5-arkitekturen er egnet for både videobehandling og trådløs kommunikasjonsadministrasjon. Ved å skyve DSP-funksjonene til FPGA, gjørAmanda prosessor kan tjene en systemadministrasjonsrolle og er fri til å implementere en trådløs kommunikasjonsstabel. Som bådeAmanda og FPGA har tilgang til det eksterne minnet, kan data raskt utveksles mellom systemets prosessorer og komponenter.

Bilde av infotainment FPGA-co-prosessorarkitektur eksempel 2.

Bilde av infotainment FPGA-co-prosessorarkitektur eksempel 2.

Den andre infotainmenten i figur 6 fremhever FPGAs evne til å adressere både innkommende høyhastighets analoge data og håndtering av komprimering og koding som trengs for videoutrustninger. Faktisk kan all denne funksjonaliteten skyves inn i FPGA, og gjennom bruk av parallell behandling kan disse adresseres i sanntid.

Ved å inkludere en FPGA i en eksisterende maskinvarearkitektur, kan den påviste ytelsen til den eksisterende maskinvaren kombineres med fleksibilitet og fremtidssikring. Selv innenfor eksisterende systemer gir co-prosessorarkitekturen alternativer til designere, som ellers ikke ville være tilgjengelige [6].

Raske prototypefordeler

I sitt hjerte strever den raske prototypeprosessen for å dekke en betydelig mengde produktutviklingsområde ved å utføre oppgaver parallelt, identifisere "feil" og designproblemer raskt, og validere data- og signalveier, spesielt de som er innenfor et prosjekts kritiske vei. For at denne prosessen virkelig skal produsere strømlinjeformede, effektive resultater, må det imidlertid være tilstrekkelig kompetanse på de nødvendige prosjektområdene.

Tradisjonelt betyr dette at det må være en maskinvareingeniør, en programvareintegrasjons- eller DSP-ingeniør og en HDL-ingeniør. Nå er det mange tverrfaglige fagpersoner, som kanskje kan tilfredsstille flere roller; Imidlertid er det fortsatt store prosjektkostnader involvert i å koordinere denne innsatsen.

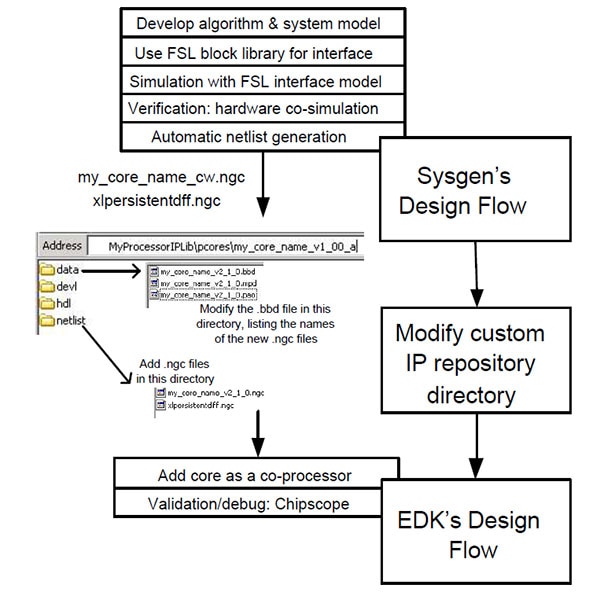

I sin artikkel, En FPGA-basert plattform for rask prototyping for wavelet-co-prosessorer, fremmer forfatterne ideen om at bruk av en co-prosessorarkitektur tillater en enkelt DSP-ingeniør å oppfylle alle disse rollene, effektivt og virkningsfullt. For denne studien begynte teamet å designe og simulere ønsket DSP-funksjonalitet i MATLABs Simulink-verktøy. Dette tjente to primære funksjoner, ved at det, 1) verifiserte ønsket ytelse gjennom simulering, og 2) fungerte som en grunnlinje som fremtidige designvalg kunne sammenlignes og refereres til.

Etter simulering ble kritiske funksjoner identifisert og delt inn i forskjellige kjerner - dette er soft-core komponenter og prosessorer som kan syntetiseres i en FPGA. Det viktigste trinnet under dette arbeidet var å definere grensesnittet mellom disse kjernene og komponentene og sammenligne ytelsen til datautveksling mot ønsket, simulert ytelse. Denne designprosessen er nøye tilpasset Xilinx sin designflyt for integrerte systemer og er oppsummert i figur 7 nedenfor.

Figur 7: Implementeringsdesignflyt.

Figur 7: Implementeringsdesignflyt.

Ved å dele systemet inn i syntetiserbare kjerner, kan DSP-ingeniøren fokusere på de mest kritiske sidene ved signalbehandlingskjeden. Hun / han trenger ikke å være ekspert på maskinvare eller HDL for å modifisere, rute eller implementere forskjellige soft-core prosessorer eller komponenter i FPGA. Så lenge designeren er klar over grensesnittet og dataformatene, har de full kontroll over signalbanene og kan avgrense systemets ytelse.

Erfaringsmessige (empiriske) funn – studien om den frittstående (diskrete) cosinustransformasjonen

De erfaringsmessige (empiriske) funnene bekreftet ikke bare fleksibiliteten som co-prosessorarkitekturen benyttet for den innebygde systemdesigneren, men viste også de ytelsesfremmende alternativene som er tilgjengelige med moderne FPGA-verktøy. Forbedringer, som de som er nevnt nedenfor, er kanskje ikke tilgjengelige eller kan ha mindre innvirkning på andre maskinvarearkitekturer. Den frittstående (diskrete) cosinustransformasjonen (DCT) ble valgt som en beregningsintensiv algoritme, og dens progresjon fra en C-basert implementasjon til en HDL-basert implementasjon var kjernen i disse funnene. DCT ble valgt siden denne algoritmen brukes i digital signalbehandling for mønstergjenkjenning og filtrering [8]. De empiriske funnene var basert på en laboratorieøvelse, som ble fullført av forfatteren og kollegene, for å oppnå Xilinx Alliance Partner-sertifisering for 2020 - 2021.

Følgende verktøy og enheter ble brukt i dette arbeidet:

- Vivado HLS v2019

- Enheten for vurdering og simulering var xczu7ev-ffvc1156-2-e

Fra og med den C-baserte implementeringen godtar DCT-algoritmen to matriser med 16-biters tall; matrise “a” er inngangsmatrisen til DCT, og matrise “b” er utgangssamlingen fra DCT. Databredden (DW) er derfor definert som 16, og antall elementer i matriser (N) er 1024 / DW, eller 64. Til slutt er størrelsen på DCT-matrisen (DCT_SIZE) satt til 8, noe som betyr at en 8 x 8 matrise brukes.

Etter utgangspunktet for denne artikkelen, gjør den C-baserte algoritmeimplementeringen designeren i stand til raskt å utvikle og validere algoritmens funksjonalitet. Selv om det er et viktig hensyn, plasserer denne valideringen funksjonalitet til en høyere vekting enn utføringstid. Denne vektingen er tillatt, siden den endelige implementeringen av denne algoritmen vil være i en FPGA, hvor maskinvareakselerasjon, looputrulling og andre teknikker er lett tilgjengelige.

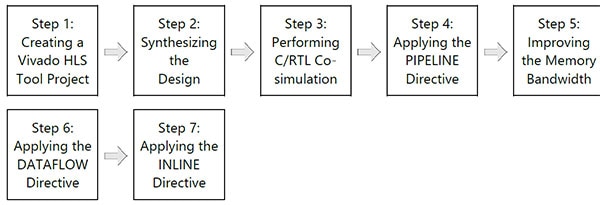

Figur 8: Xilinx Vivado HLS designflyt.

Figur 8: Xilinx Vivado HLS designflyt.

Når DCT-koden ble opprettet iVivado HLS verktøy som et prosjekt, er neste trinn å begynne å syntetisere design for FPGA-implementering. Det er på dette neste trinnet hvor noen av de mest effektive fordelene ved å flytte en algoritmes kjøring fra en mikrokontroller (MCU) til en FPGA blir tydeligere – som en referanse tilsvarer dette trinnet Systemadministrasjon med Microcontroller-milepælen diskutert ovenfor.

Moderne FPGA-verktøy tillater en rekke optimaliseringer og forbedringer som i stor grad forbedrer ytelsen til komplekse algoritmer. Før du analyserer resultatene, er det noen viktige begreper du må huske på:

- Latens - Antall klokkesykluser som kreves for å utføre alle iterasjoner av sløyfen [10]

- Intervall - Antall klokkesykluser før neste iterasjon av en sløyfe begynner å behandle data [11]

- BRAM - Blokkere minne for tilfeldig tilgang

- DSP48E - Digital Signal Processing Slice for UltraScale-arkitekturen

- FF - Flipflop

- LUT – Oppslagstabell

- URAM – Unified Random-Access Memory (kan bestå av en enkelt transistor)

|

||||||||||||||||||||||||||||||||||||||||

Tabell 1: Optimeringsfunn for FPGA-algoritmeutførelse (latens og intervall).

|

Tabell 2: Optimeringsfunn for FPGA-algoritmeutførelse (ressursbruk).

Standard

Standard optimaliseringsinnstilling kommer fra det uendrede resultatet av å oversette den C-baserte algoritmen til syntetiserbar HDL. Ingen optimaliseringer er aktivert, og dette kan brukes som en ytelsesreferanse for å bedre forstå de andre optimaliseringene.

Rørledning indre sløyfe

Rørlednings-direktivet instruerer Vivado HLS om å rulle ut de indre sløyfene slik at nye data kan begynne å bli behandlet mens eksisterende data fortsatt er i rørledningen. Dermed trenger ikke nye data å vente på at de eksisterende dataene er fullført før behandlingen kan begynne.

Rørledning ytre sløyfe

Ved å anvende Rørlednings-direktivet på den ytre sløyfen, er den ytre sløyfens drift nå rørledet. De indre sløyfenes operasjoner skjer imidlertid nå samtidig. Både latensen og intervalltiden kuttes i to ved å påføre dette direkte på den ytre sløyfen.

Matrisepartisjon

Dette direktivet kartlegger innholdet i sløyfene til matriser og flater dermed ut all minnetilgang til enkeltelementer i disse matrisene. Ved å gjøre dette forbrukes det mer RAM, men igjen kuttes kjøretiden for denne algoritmen i to.

Dataflyt

Dette direktivet gjør det mulig for konstruktøren å angi målantallet klokkesykluser mellom hver inndataavlesning. Dette direktivet støttes bare for funksjoner på øverste nivå. Bare sløyfer og funksjoner som eksponeres for dette nivået, vil dra nytte av dette direktivet.

Rekke (in-line)

REKKE (IN-LINE)-direktivet flater ut alle sløyfer, både indre og ytre. Både rad- og kolonneprosesser kan nå kjøres samtidig. Antall nødvendige klokkesykluser holdes på et minimum, selv om dette forbruker flere FPGA-ressurser.

Konklusjon

Co-prosessorens maskinvarearkitektur gir den integrasjonsdesigneren en plattform med høy ytelse som opprettholder sin designfleksibilitet gjennom hele utviklingen og tidligere produktutgivelser. Ved først å validere algoritmer i C eller C++ kan prosesser, data- og signalbaner og kritisk funksjonalitet verifiseres på relativt kort tid. Deretter, ved å oversette de prosessorintensive algoritmene til co-prosessorsens FPGA, kan designeren nyte fordelene med maskinvareakselerasjon og en mer modulær design.

Skulle deler bli foreldet eller optimaliseringer være nødvendig, kan den samme arkitekturen tillate disse endringene. Nye mikrokontrollere (MCU-er) og nye FPGA-er kan monteres i konstruksjonen, samtidig som grensesnittene kan forbli relativt uberørte. I tillegg, siden både mikrokontrollere (MCU-er) og FPGA er feltoppdaterbare, kan brukerspesifikke endringer og optimaliseringer brukes i felten og eksternt.

Til slutt blander denne arkitekturen utviklingshastigheten og tilgjengeligheten til en mikrokontroller (MCU) med ytelsen og utvidelsesmulighetene til en FPGA. Med optimaliseringer og ytelsesforbedringer tilgjengelig på hvert utviklingstrinn, kan co-prosessorarkitekturen imøtekomme behovene til selv de mest utfordrende kravene – både for dagens design og utover.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.